使用TCL腳本快速創建Quartus工程

在剛開始學習FPGA的時候,使用Quartus Prime的GUI界面創建工程是一個再平常不過的事兒,但是隨著項目的增多,有很多項目可能會用到之前項目的代碼,如果用GUI界面添加代碼也可以,但是總覺得這種方法效率太低(點擊New Project Wizard->選擇工程目錄,輸入工程名,頂層文件名->添加工程代碼及所需的IP文件->選擇器件型號->管腳約束……)。

后面在網上找相關的更高效的方法,最終找到了一種使用TCL腳本快速創建Quartus工程的方法,這里直接貼TCL腳本的一個示例:

點擊查看代碼

# 創建工程

project_new -revision TGLV26 -overwrite TGLV26

# 添加源碼文件

# 頂層文件

set_global_assignment -name VERILOG_FILE ../src/TGTop.v

# a文件夾

set_global_assignment -name VERILOG_FILE ../src/a/xxx.v

set_global_assignment -name VERILOG_FILE ../src/a/xxx.v

set_global_assignment -name VERILOG_FILE ../src/a/xxx.v

set_global_assignment -name VERILOG_FILE ../src/a/xxx.v

set_global_assignment -name VERILOG_FILE ../src/a/xxx.v

set_global_assignment -name VERILOG_FILE ../src/a/xxx.v

set_global_assignment -name VERILOG_FILE ../src/a/xxx.v

set_global_assignment -name VERILOG_FILE ../src/a/xxx.v

set_global_assignment -name VERILOG_FILE ../src/a/xxx.v

# b文件夾

set_global_assignment -name VERILOG_FILE ../src/b/xxx.v

set_global_assignment -name VERILOG_FILE ../src/b/xxx.v

set_global_assignment -name VERILOG_FILE ../src/b/xxx.v

set_global_assignment -name VERILOG_FILE ../src/b/xxx.v

set_global_assignment -name VERILOG_FILE ../src/b/xxx.v

set_global_assignment -name VERILOG_FILE ../src/b/xxx.v

set_global_assignment -name VERILOG_FILE ../src/b/xxx.v

set_global_assignment -name VERILOG_FILE ../src/b/xxx.v

set_global_assignment -name VERILOG_FILE ../src/b/xxx.v

# Position文件夾

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

set_global_assignment -name VERILOG_FILE ../src/c/xxx.v

# TransportCtr文件夾

set_global_assignment -name VERILOG_FILE ../src/d/xxx.v

set_global_assignment -name VERILOG_FILE ../src/d/xxx.v

set_global_assignment -name VERILOG_FILE ../src/d/xxx.v

set_global_assignment -name VERILOG_FILE ../src/d/xxx.v

set_global_assignment -name VERILOG_FILE ../src/d/xxx.v

set_global_assignment -name VERILOG_FILE ../src/d/xxx.v

set_global_assignment -name QXP_FILE ../src/d/xxx.qxp

set_global_assignment -name VERILOG_FILE ../src/d/xxx.v

set_global_assignment -name VERILOG_FILE ../src/d/xxx.v

# 添加IP核

set_global_assignment -name QSYS_FILE ../ip/xxx.qsys

set_global_assignment -name QIP_FILE ../ip/RAM/xxx.qip

set_global_assignment -name QIP_FILE ../ip/ID/xxx.qip

set_global_assignment -name QIP_FILE ../ip/PLL/xxx.qip

set_global_assignment -name QSYS_FILE ../ip/DUALBOOT/xxx.qsys

# 頭文件

set_global_assignment -name SOURCE_FILE ../src/xxx.h

set_global_assignment -name SOURCE_FILE ../src/xxx.h

# 添加時序約束文件

set_global_assignment -name SDC_FILE ../src/xxx.sdc

# TCL腳本

set_global_assignment -name TCL_SCRIPT_FILE ../src/xxx.tcl

set_global_assignment -name TCL_SCRIPT_FILE ../src/xxx.tcl

set_global_assignment -name TCL_SCRIPT_FILE ../src/xxx.tcl

# 設置工程的頂層模塊

set_global_assignment -name TOP_LEVEL_ENTITY TGTop

#------------------GLOBAL--------------------#

set_global_assignment -name FAMILY "MAX 10"

set_global_assignment -name DEVICE 10M16SAU169I7G

set_global_assignment -name EXTERNAL_FLASH_FALLBACK_ADDRESS 00000000

set_global_assignment -name USE_CONFIGURATION_DEVICE OFF

set_global_assignment -name INTERNAL_FLASH_UPDATE_MODE "DUAL IMAGES"

set_global_assignment -name FLOW_ENABLE_POWER_ANALYZER ON

# 輸出bitstream文件夾

set_global_assignment -name PROJECT_OUTPUT_DIRECTORY output_files

set_global_assignment -name VERILOG_INPUT_VERSION SYSTEMVERILOG_2005

# 設置seed值

set_global_assignment -name SEED 7

# 預處理腳本

set_global_assignment -name PRE_FLOW_SCRIPT_FILE "quartus_sh:../src/VersionGen.tcl"

# 后處理腳本

set_global_assignment -name POST_FLOW_SCRIPT_FILE "quartus_sh:../src/BitstreamGen.tcl"

# 并行編譯可使用的最大處理器數

set_global_assignment -name NUM_PARALLEL_PROCESSORS ALL

#------------------ 引腳約束 --------------------#

source "../src/xxx.tcl"

#--------------------------------------------#

# 將所有約束寫入qsf文件

export_assignments

# 關閉工程

# project_close

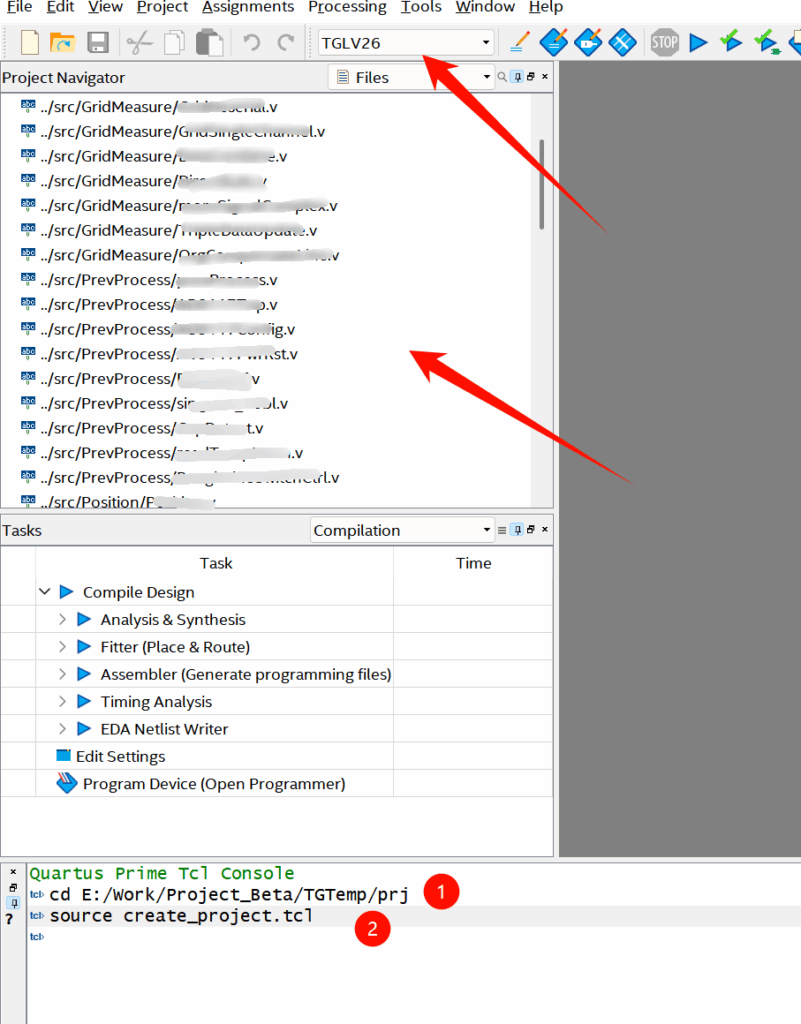

只需創建一個工程文件夾,并在TCL腳本中描述所需的verilog源碼文件和IP文件的路徑,然后再打開quartus軟件,并打開TCL Console窗口,在指令行中輸入cd E:/Work/Project_Beta/TGTemp/prj(這里改為腳本所在文件路徑),然后輸入source xxx.tcl(xxx代表tcl腳本的文件名),即可快速創建工程,具體如下圖: