這個案例1-【友晶科技Terasic】基于FPGA實現LTC2308控制器的設計——總概述里面的fifo是調用的Altera現成的IP(adc_data_fifo.v),現在直接用前面掰開揉碎講 FIFO(同步FIFO和異步FIFO)設計的 async_fifo 替換掉它Altera FIFO IP:

具體的做法是:

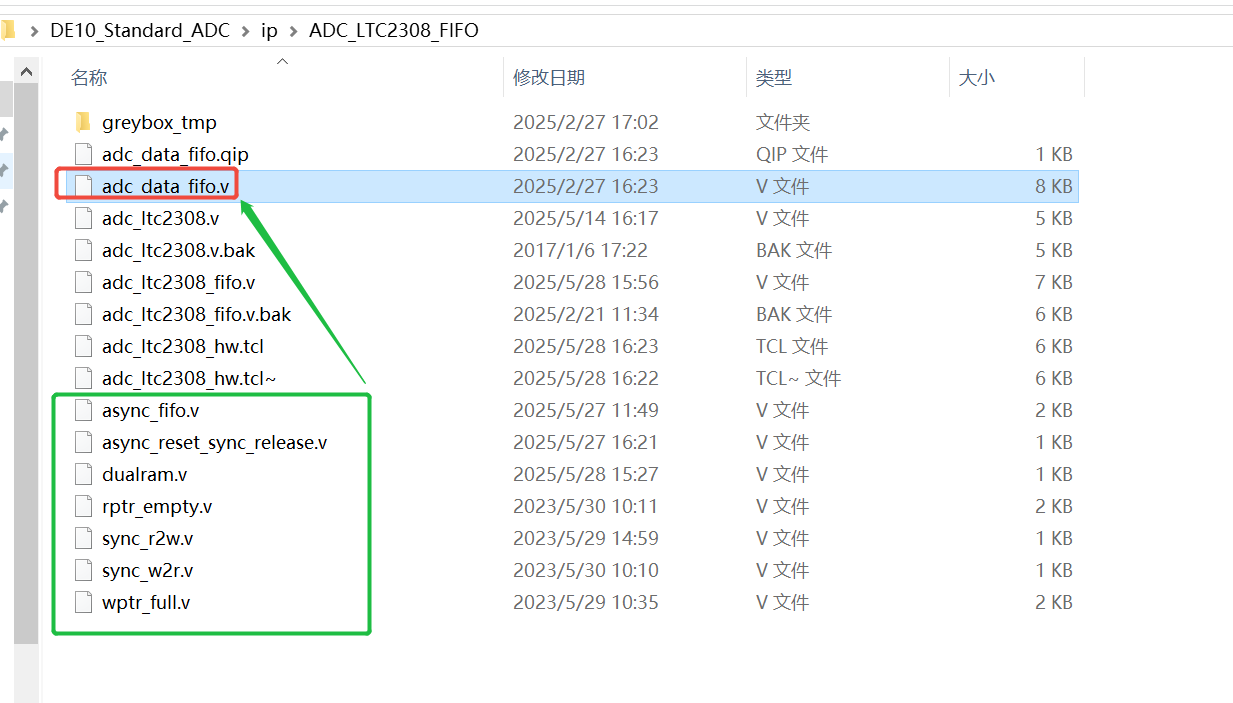

1. 刪除adc_data_fifo.v文件, 增加async_fifo.v, async_reset_sync_release.v,dualram.v,rptr_empty.v,sync_r2w.v,sync_w2r.v,wptr_full.v 7個文件。

2. 在自定義 LTC2308 控制器IP 的top文件adc_ltc2308_fifo.v當中做如下修改:

3. 記得將自定義IP ADC_LTC2308_FIFO 重新生成一遍,步驟參考:

9-【友晶科技Terasic】基于FPGA實現LTC2308控制器的設計——自定義IP設計步驟(Avalon MM)(17.1)

4. 重新生成Qsys系統。步驟參考下面鏈接的Qsys設計部分:

8-【友晶科技Terasic】基于FPGA實現LTC2308控制器的設計——Quartus工程創建(17.1) 主要是參考該文章中 adc_ltc2308 IP 的設置部分。

5. 重新generate Qsys系統。

6. 重新編譯Quartus文件,下載sof文件到DE10-Standard開發板。

7. Nios 工程代碼無需更改,直接run Nios II 工程代碼,按照下文章去測試:

1-【友晶科技Terasic】基于FPGA實現LTC2308控制器的設計——總概述

無

浙公網安備 33010602011771號

浙公網安備 33010602011771號