vhdl筆記

考試真題

一、填空題(共20分)

1.EDA的含義是(電子設(shè)計(jì)自動化),VHDL的含義是(超高速硬件描述語言)

2.請列出三個(gè)VHDL語言的數(shù)據(jù)類型。利于實(shí)數(shù)數(shù)據(jù)類型、位數(shù)據(jù)類型等。(整型)(字符型)(字符串型)

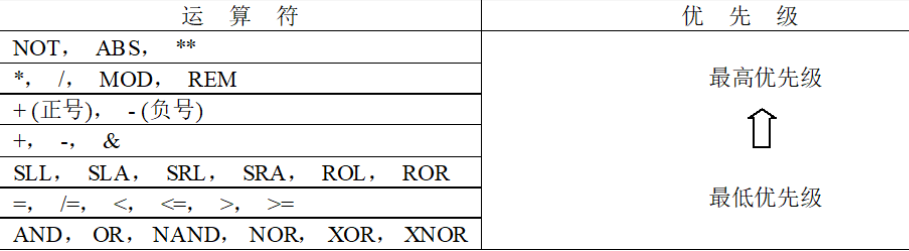

3.VHDL的運(yùn)算符中,優(yōu)先級別最低的是(邏輯運(yùn)算符),優(yōu)先級別最高的是(NOT,ABS)

4.試定義一個(gè)變量A,數(shù)據(jù)類型為4位標(biāo)準(zhǔn)矢量:(variable A:STD_LOGIC_VECRTOR(3 DOWNTO 0)??

5.在VHDL的數(shù)據(jù)對象中,(信號)(變量)可以多次賦予不同的值,只能在定義是復(fù)值的是(常量)

6.VHDL的子程序有(函數(shù))和(常量)兩種

7.VHDL源程序的文件名應(yīng)當(dāng)與(實(shí)體名)相同,否則無法通過編譯

8.設(shè)D0為‘0’,D1為‘0’,D2為‘1’,D3為‘0’,D3&D2&D1&D0的運(yùn)算表達(dá)結(jié)果是(0100)

9.使用quartusII軟件中時(shí),文本編輯文件的后綴名是:vhd,波形仿真文件的后綴名稱是:vwf

二、簡答題(20分,共4題,每道題5分)

1.簡述cpld與fpga的異同,在實(shí)際應(yīng)用是該如何選擇?

答:CPLD更加適合完成各種算法和組合邏輯,F(xiàn)PGA更加適合于完成時(shí)序邏輯。換句話說,F(xiàn)PGA更加適合于觸發(fā)器豐富的結(jié)構(gòu),而CPLD更加適合于觸發(fā)器有限而乘積項(xiàng)豐富的結(jié)構(gòu)。

CPLD的連續(xù)式布線結(jié)構(gòu)決定了它的時(shí)序延遲是均勻的和可預(yù)測的,而FPGA的分段式補(bǔ)線結(jié)構(gòu)決定了其延遲的不可預(yù)測性。

CPLD比FPGA使用起來更加方便。CPLD的編程采用E2PROM或者FASTFLASH技術(shù),無需外部存儲器芯片,使用簡單。而FPGA的編程信息需要存放在外部存儲器上,使用方法復(fù)雜。

2.簡述VHDL語言和計(jì)算機(jī)C語言的區(qū)別

答:VHDL是硬件描述語言,面向硬件的。用于CPLD、FPGA等大規(guī)模可編程邏輯器件的。而C語言主要是面向軟件的,是計(jì)算機(jī)編程。適用于普通計(jì)算機(jī)的,以及單片機(jī),DSP等等。

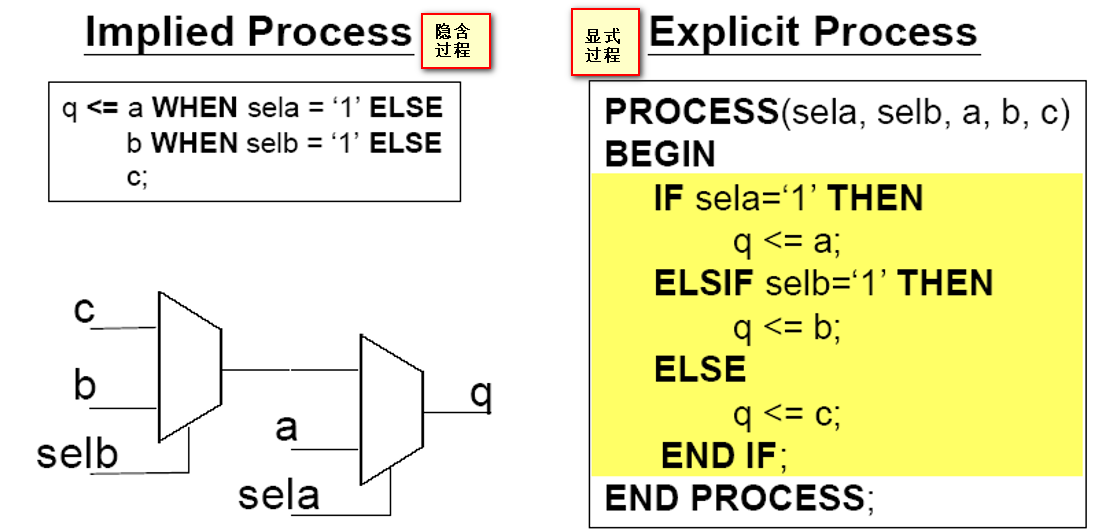

3.簡述when_else條件信號賦值語句和if_else順序語句的異同。

答:WHEN_ELSE條件信號賦值語句中無標(biāo)點(diǎn),只有最后有分號;必須成對出現(xiàn):是并行語句,必須放在結(jié)構(gòu)體中。

IF_ELSE順序語句中有分號;是順序語句,必須放在進(jìn)程中。

4,簡述quartusII的設(shè)計(jì)流程

建立工作庫文件夾:輸入設(shè)計(jì)項(xiàng)目原理圖/VHDL文件;將設(shè)計(jì)項(xiàng)目設(shè)置成PROJECT;選擇目標(biāo)器件;編譯;引腳鎖定并編譯;編程下載/配置。

:原理圖/HDL文本輸入--->功能仿真--->綜合--->適配--->時(shí)序仿真--->編程下載--->硬件測試

三、VHDL程序設(shè)計(jì)題目(60分)

1.用并行信號賦值語句設(shè)計(jì)4選1數(shù)據(jù)選擇器。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DEMO IS

PORT(

I0,I1,I2,I3: IN STD_LOGIC;

CH0,CH1: IN STD_LOGIC;

OUTPUT: OUT STD_LOGIC;

);

END DEMO;

ARCHITECTURE BEHAVE OF DEMO IS

SIGNAL SEL:STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

SEL<=CH1&CH0;

OUTPUT<=I0 WHEN SEL="00" ELSE

I1 WHEN SEL="01" ELSE

I2 WHEN SEL="10" ELSE

I3 WHEN SEL="11" ELSE

'0';

END BEHAVE;

2.編寫一個(gè)數(shù)值比較器VHDL程序的進(jìn)程,要求使能信號g低電平時(shí)比較器開始工作,輸入信號p=q,輸出equ為‘0’,否則為‘1’

PROCESS(P,Q,G)

BEGIN

IF G='0' THEN

IF P=Q THEN

EQU<='0';

ELSE

EQU<='1';

END IF;

ELSE

EQU<='1';

END IF;

END PROCESS;

3.在程序包中設(shè)計(jì)一個(gè)功能為四舍五入的過程。

函數(shù)定義應(yīng)由兩部分組成,即函數(shù)首和函數(shù)體.

在進(jìn)程和結(jié)構(gòu)體中不必定義函數(shù)首,而在程序包中必須定義函數(shù)首.

--過程

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

PACKAGE PACK IS

PROCEDURE SUM(

A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);B:OUT STD_LOGIC);

END PACK;

PACKAGE BODY PACK IS

PROCEDURE SUM(

A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);B:OUT STD_LOGIC) IS

BEGIN

IF A="0100"OR A<"0100" THEN B<='0';

ELSE B<='1';

END IF;

END PROCEDURE SUM;

END PACK;

--函數(shù)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

PACKAGE PACK IS

FUNCTION SUM(A:STD_LOGIC_VECTOR(3 DOWNTO 0);B:STD_LOGIC)RETURN STD_LOGIC;

END PACKAGE;

PACKAGE BODY PACK IS

FUNCTION SUM(A:STD_LOGIC_VECTOR(3 DOWNTO 0);B:STD_LOGIC)RETURN STD_LOGIC IS

BEGIN

IF A="0100" OR A<"0100" THEN B<='0';

ELSE B<='1';

END IF;

RETURN B;

END FUNCTION SUM;

END PACK;

4.設(shè)計(jì)一個(gè)異步清零的10進(jìn)制計(jì)數(shù)器,并且在數(shù)碼管上顯示

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DEMO IS

PORT(

CLK,RES:IN STD_LOGIC;

LEDOUT:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

);

END DEMO;

ARCHITECTURE BEHAVE OF DEMO IS

SIGNAL CNT :STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(CLK,RES)

BEGIN

IF RES='1' THEN

CNT<=(OTHERS>='0');

ELSIF (CLK'EVENT AND CLK='1')THEN

IF(CNT="1001")THEN

CNT<="0000";

ELSE

CNT<=CNT+'1';

END IF;

END IF;

END PROCESS;

LEDOUT<="1110111"WHEN CNT="0000"ELSE

"0100100"WHEN CNT="0001"ELSE

"1011101"WHEN CNT="0010"ELSE

"1011011"WHEN CNT="0011"ELSE

"0111010"WHEN CNT="0100"ELSE

"1101011"WHEN CNT="0101"ELSE

"0101111"WHEN CNT="0110"ELSE

"1010010"WHEN CNT="0111"ELSE

"1111111"WHEN CNT="1000"ELSE

"1111101"WHEN CNT="1001"ELSE

"0000000";

END BEHAVE;

---a---

- -

b c

- -

---d---

- -

e f

- -

---g---

5.設(shè)計(jì)一個(gè)由6個(gè)觸發(fā)器構(gòu)成的一步計(jì)數(shù)器,采用元件例化的方式生成

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY D_FF IS

PORT(

D,CLK_S:IN STD_LOGIC;

Q:OUT STD_LOGIC;

NQ:OUT STD_LOGIC

);

END ENTITY D_FF;

ARCHITECTURE A_RS_FF OF D_FF IS

BEGIN

BIN_P_RS_FF:PROCESS(CLK_S)

BEGIN

IF CLK_S'EVENT AND CLK_S='1' THEN Q<=D;NQ<=NOT D;

END IF;

END PROCESS;

END ARCHITECTURE A_RS_FF;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY demo12 IS

PORT(

CLK:IN STD_LOGIC;

Q:OUT STD_LOGIC_VECTOR(5 DOWNTO 0)

);

END demo12;

ARCHITECTURE BEHAVE OF demo12 IS

COMPONENT D_FF IS

PORT(

D,CLK_S:IN STD_LOGIC;

Q:OUT STD_LOGIC;

NQ:OUT STD_LOGIC

);

END COMPONENT;

SIGNAL S:STD_LOGIC_VECTOR(5 DOWNTO 0);

BEGIN

U0:D_FF PORT MAP(S(0),CLK,Q(0),S(0));

U1:D_FF PORT MAP(S(1),S(0),Q(1),S(1));

U2:D_FF PORT MAP(S(2),S(1),Q(2),S(2));

U3:D_FF PORT MAP(S(3),S(2),Q(3),S(3));

U4:D_FF PORT MAP(S(4),S(3),Q(4),S(4));

U5:D_FF PORT MAP(S(5),S(4),Q(5),S(5));

END BEHAVE;

標(biāo)準(zhǔn)函數(shù),它用于將整數(shù)轉(zhuǎn)換為 std_logic_vector 類型:

my_signal <= conv_std_logic_vector(255, 8); -- 結(jié)果為 "11111111"

在這個(gè)例子中,整數(shù) 255 被轉(zhuǎn)換為一個(gè) 8 位寬的 std_logic_vector,結(jié)果是 "11111111"。

將整數(shù)或?qū)崝?shù)轉(zhuǎn)換為 std_logic_vector 類型的過程:

to_stdlogicvector(255, my_vector); -- my_vector 將被賦值為 "11111111"

請注意,to_stdlogicvector 過程需要在進(jìn)程內(nèi)部調(diào)用,因?yàn)樗婕暗叫盘栙x值。

這個(gè)函數(shù)用于將 std_logic_vector 類型的信號轉(zhuǎn)換為 BIT_VECTOR 類型。BIT_VECTOR 是一個(gè)類似數(shù)組的類型,其中的元素可以是 '0'、'1' 或 'U'(未初始化),它通常用于表示二進(jìn)制數(shù):

my_slv <= "10101010"; -- 將std_logic_vector初始化為特定的值

my_bv <= TO_BITVECTOR(my_slv); -- 將std_logic_vector轉(zhuǎn)換為BIT_VECTOR

四、課本

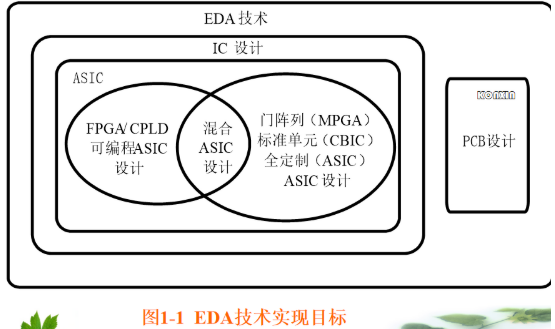

1.1:EDA技術(shù)與ASIC設(shè)計(jì)和FPGA開發(fā)的關(guān)系:利用EDA技術(shù)進(jìn)行電子系統(tǒng)設(shè)計(jì)的最后目標(biāo)是完成專用集成電路ASIC的設(shè)計(jì)與實(shí)現(xiàn)。

FPGA在ASIC設(shè)計(jì)中的用途:FPGA實(shí)現(xiàn)ASIC設(shè)計(jì)的現(xiàn)場可編程器件。

1.7:CPLD是基于乘積項(xiàng)的可編程邏輯結(jié)構(gòu),F(xiàn)PGA是基于查找表的可編程邏輯結(jié)構(gòu)

考試學(xué)習(xí)

第一章:EDA前言知識

EDA:電子設(shè)計(jì)自動化(Electronic Design Automation)

HDL:硬件描述語言(Hardware Description Language)

ISP:在系統(tǒng)可編程(In System Programmability)

單片機(jī)和FPGA比,不同之處在于,單片機(jī)是用已知的硬件來構(gòu)建系統(tǒng),主要是寫軟件。而FPGA是硬件“未知”(用EDA工具來設(shè)計(jì)),軟件也要自己寫。

EDA發(fā)展階段

- 計(jì)算機(jī)輔助設(shè)計(jì)(Computer Assist Design,CAD)(20世紀(jì)70年代)

- 計(jì)算機(jī)輔助工程設(shè)計(jì)(Computer Assist Engineering Design,CAED)(20世紀(jì)80年代)

- 電子設(shè)計(jì)自動化(Electronic Design Automation,EDA)(20世紀(jì)90年代)

- 超大規(guī)模可編程邏輯器件(可編程ASIC):主流器件:FPGA/CPLD

- 半定制或全定制ASIC

- 混合ASIC

基于EDA軟件的FPGA/CPLD設(shè)計(jì)流程:

原理圖/HDL 文本輸入--->功能仿真--->綜合--->適配--->編程下載--->硬件測試

PLD:可編程邏輯器件

CPLD:復(fù)雜可編程邏輯器件

FPGA:現(xiàn)場可編程門陣列

FPGA:

- 可編程邏輯單元

- 可編程輸入/輸出單元

- 可編程連線

CPLD:

- 可編程邏輯宏單元

- 可編程輸入輸出單元

- 可編程內(nèi)部連線

第三章:CPLD與FPGA結(jié)構(gòu)與應(yīng)用

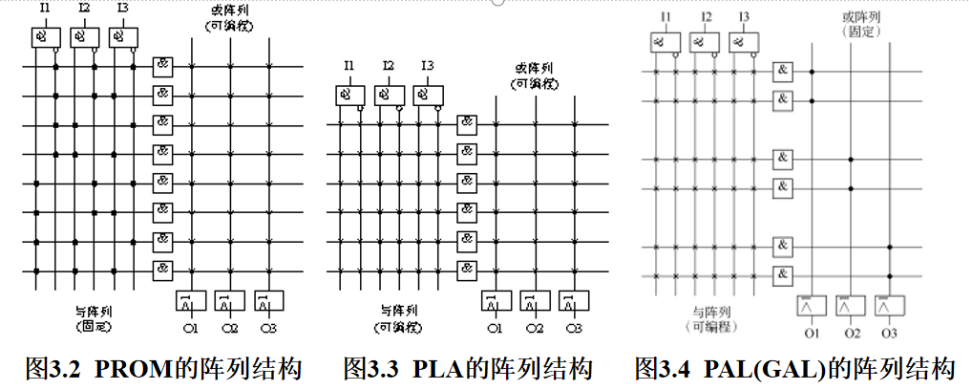

1.PLD

它由輸入緩沖器、與陣列、或陣列、輸出緩沖器等4部分功能電路組成

20世紀(jì)70年代,PLD主要是PROM和PLA

- PROM(可編程只讀存儲器):與門陣列固定、或門陣列可編程(熔絲工藝,一次性編程使用)

- PLA(可編程邏輯陣列):與門陣列可編程、或門陣列可編程(熔絲工藝,一次性編程使用)

- PAL(可編程陣列邏輯):與門陣列可編程、或門陣列固定

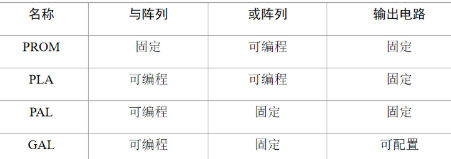

2.FPGA

FPGA器件的內(nèi)部結(jié)構(gòu)為LCA(邏輯單元陣列)

LCA:

- 周邊的IOB(IO Block)(可編程輸入/輸出模塊)

- 核心陣列的CLB(Configurable Logic Block)(可配置邏輯塊)

- PI(可編程內(nèi)部連線)(Programmable Interconnect)

- CLB:CLB是FPGA的基本邏輯單元,其內(nèi)部又可以分為組合邏輯和寄存器兩部分。組合邏輯電路實(shí)際上是一個(gè)多變量輸入的PROM陣列,可以實(shí)現(xiàn)多變量任意函數(shù);而寄存器電路是由多個(gè)觸發(fā)器及可編程輸入、輸出和時(shí)鐘端組成的。在FPGA中,所有的邏輯功能都是在CLB中完成的。

- IOB為芯片內(nèi)部邏輯和芯片外部的輸入端/輸出端提供接口,可編程為輸入、輸出和雙向I/O 3種方式。

- FPGA依靠對PI的編程,將各個(gè)CLB和IOB有效地組合起來,實(shí)現(xiàn)系統(tǒng)的邏輯功能。

工作形式:采用基于SRAM的查找表邏輯形式結(jié)構(gòu)

一個(gè)N輸入的查找表,需要SRAM存儲N個(gè)輸入構(gòu)成的真值表,需要2^N個(gè)SRAM單元。

A,B,C,D由FPGA芯片的管腳輸入后進(jìn)入可編程連線,作為地址線連到LUT,LUT中已經(jīng)事先寫入了所有可能的邏輯結(jié)果,通過地址查找到相應(yīng)的數(shù)據(jù)然后輸出,這樣組合邏輯就實(shí)現(xiàn)了

3.CPLD

- 邏輯陣列單元LAB

- 可編程IO單元

- 可編程內(nèi)部互聯(lián)資源EAB(嵌入陣列塊)

CPLD的基本結(jié)構(gòu)是由一個(gè)二維的邏輯塊陣列組成的,它是構(gòu)成CPLD器件的邏輯組成核心,還有多個(gè)I/O塊以及連接邏輯塊的互連資源。

每組邏輯單元LE(Logic Element)連接到邏輯陣列塊LAB(Logic Array Block),LAB被分成行和列,每行包含一個(gè)嵌入陣列塊EAB。LAB和EAB由快速通道互相連接。I/O單元IOE(Input/Output Elements)位于行通道和列通道兩端。

嵌入陣列由一系列嵌入陣列塊EAB構(gòu)成。實(shí)現(xiàn)存儲功能時(shí),每個(gè)EAB提供2048比特,可以用來完成RAM、ROM、雙口RAM或者FIFO功能。實(shí)現(xiàn)邏輯功能時(shí),每個(gè)EAB可以提供100~600門以實(shí)現(xiàn)復(fù)雜的邏輯功能,如實(shí)現(xiàn)乘法器、微控制器、狀態(tài)機(jī)和DSP(數(shù)字信號處理)功能。EAB可以單獨(dú)使用或多個(gè)EAB聯(lián)合使用以實(shí)現(xiàn)更強(qiáng)的功能。

邏輯陣列由邏輯陣列塊LAB構(gòu)成。每個(gè)LAB包含8個(gè)邏輯單元和一個(gè)局部連接。一個(gè)邏輯單元有一個(gè)4輸入查找表、一個(gè)可編程觸發(fā)器和一個(gè)實(shí)現(xiàn)進(jìn)位和級聯(lián)功能的專用信號路徑。

LAB按照行、列排序,構(gòu)成邏輯陣列,每個(gè)LAB由8個(gè)LE構(gòu)成,為行列兩端的輸入輸出單元IOE提供I/O端口。每個(gè)IOE包含一個(gè)雙向I/O緩沖器和一個(gè)可以用作輸入輸出寄存的觸發(fā)器,

XC3164 PC 84-4 C 的含義如下:

-

第1項(xiàng):XC3164表示器件型號。

-

第2項(xiàng):PC表示器件的封裝形式,主要有PLCC(Plastic Leaded Chip Carrier,塑料方形扁平封裝)、PQFP(Plastic Quad Flat Pack,塑料四方扁平封裝)、TQFP(Thin Quad Flat Pack,四方薄扁形封裝)、RQFP(Power Quad Flat Pack,大功率四方扁平封裝)、BGA(Bal Grid Array(Package),球形網(wǎng)狀陣列(封裝))、PGA(Ceramic Pin Grid Array(Package),陶瓷網(wǎng)狀直插陣列(封裝)等形式。

-

第3項(xiàng):84表示封裝引腳數(shù)。一般有44、68、84、100、144、160、208、240等數(shù)種,常用的器件封裝引腳數(shù)有44、68、84、100、144、160等,最大的達(dá)596個(gè)引腳。而最大用戶I/O是指相應(yīng)器件中用戶可利用的最大輸入/輸出引腳數(shù)目,它與器件的封裝引腳不一定相同。

-

第4項(xiàng):- 4表示速度等級。速度等級有兩種表示方法。在較早的產(chǎn)品中,用觸發(fā)器的反轉(zhuǎn)速率來表示,單位為MHz,一般分為-50、-70、-100、-125和-150;在較后的產(chǎn)品中用一個(gè)CLB的延時(shí)來表示,單位為ns,一般可分為-10、-8、- 6、-5、- 4、-3、-2、- 09。

-

第5項(xiàng): C表示環(huán)境溫度范圍。其中又有C——商用級(0℃~85℃)、I——工業(yè)級(- 40℃~100℃)和M——軍用級(-55℃~125℃)。

選擇題

0.若一個(gè)進(jìn)程內(nèi)同一個(gè)信號的賦值語句(<=)有多條,則前幾條不做操作,最后一條才裝載

1.一個(gè)項(xiàng)目的輸入輸出是定義在()

a.實(shí)體中 b.結(jié)構(gòu)體中 c.任何位置 d.進(jìn)程中

2.描述項(xiàng)目具有邏輯功能的是()

a.實(shí)體 B.結(jié)構(gòu)體 C.配置 D.進(jìn)程

3.關(guān)鍵字ARCHITECTURE定義的是()

A.結(jié)構(gòu)體 B.進(jìn)程 C,實(shí)體 D.配置

4.MAXPLUSII中編譯VHDL源程序時(shí)要求()

A.文件名和實(shí)體不可同名

B.文件名和實(shí)體名無關(guān)

C.文件名和實(shí)體名要相同

D.不確定

5.1987標(biāo)準(zhǔn)的VHDL語言對大小寫是

A.敏感的 B.只能用小寫 C.只能用大寫 D.不敏感

6.關(guān)于1987標(biāo)準(zhǔn)的VHDL語言中,標(biāo)識符描述正確的是()

A.必須是以英文字母開頭

B.可以使用漢字開頭

C.可以使用數(shù)字開頭

D.任何字符都可以

7.關(guān)于1987標(biāo)準(zhǔn)的VHDL語言中,標(biāo)識符描述正確的是()

A.下劃線可以連用

B.下劃線不能連用

C.不能使用下劃線

D.可以使用任何字符

8.符合1987VHDL標(biāo)準(zhǔn)的標(biāo)識符是()

A.A_2 B.A+2 C.2A D.22

9.符合1987VHDL標(biāo)準(zhǔn)的標(biāo)識符是

A.a_2_3 B.a___2 C.2_2_a D.2a

10.不符合1987VHDL標(biāo)準(zhǔn)的標(biāo)識符是

A.a_1_in B. a_in_2 C.2_a D. asd_1

11.不符合1987VHDL標(biāo)準(zhǔn)的標(biāo)識符是

A.a2b2 B.a1b1 C.ad12 D.%50

12.VHDL語言中變量中定義的位置是

A.實(shí)體中任何位置 B.實(shí)體中特定位置 C.結(jié)構(gòu)體中任意位置 D.結(jié)構(gòu)體中特定位置

13.VHDL語言中信號定義的位置是

A.實(shí)體中任何位置 B.實(shí)體中特定位置 C.結(jié)構(gòu)體中任意位置 D.結(jié)構(gòu)體中特定位置

14.變量是局部量,可以寫在

A.實(shí)體中 B.進(jìn)程中 C.線粒體中 D. 種子體中

15.變量和信號的描述正確的是

A.變量賦值號是:= B.信號賦值號是:= C.變量賦值號碼是<= D. 二者沒有區(qū)別

16.變量和信號描述正確的是

A.變量可以帶出進(jìn)程 B.信號可以帶出進(jìn)程 C.信號不可以帶出進(jìn)程 D.二者沒有區(qū)別

- 關(guān)于VHDL類型,正確得是

A.數(shù)據(jù)類型不同不能進(jìn)行運(yùn)算

B.數(shù)據(jù)類型相同才能進(jìn)行運(yùn)算

C.數(shù)據(jù)類型相同或者相符就可以進(jìn)行計(jì)算

D.運(yùn)算與數(shù)據(jù)類型無關(guān)

18.下面數(shù)據(jù)中屬于實(shí)數(shù)的是

A. 4.2 B. 3 C. ‘1’ D. “11011”

19.下面數(shù)據(jù)中屬于位矢量的是

A. 4.2 B. 3 C. ‘1’ D. “11011”

20.關(guān)于VHDL數(shù)據(jù)類型,正確的是

A.用戶不能定義子類型 B.用戶可以定義子類型

C.用戶可以定義任意類型的數(shù)據(jù) D.前面三個(gè)答案都是錯(cuò)誤的

- 可以不必聲明而直接引用的數(shù)據(jù)類型是

A.STD_LOGIC B.STD_LOGIC_VECTOR C.BIT D.前面三個(gè)答案都是錯(cuò)誤的

- STD_LOGIC_1164中定義的高阻是

A.X B. x C. z D.Z

23.STD_LOGIC_1164中字符H定義的是

A.弱信號1 B.弱信號0 C.沒有這個(gè)定義 D. 初始值

1-5:ABACD 6-10:ABAAC 11-15:DDDBA

學(xué)習(xí)基本結(jié)構(gòu)

VHDL的基本設(shè)計(jì)單元結(jié)構(gòu):程序包說明、實(shí)體說明、結(jié)構(gòu)體說明三部分。

-- 庫、程序包的說明調(diào)用

Library IEEE;

use IEEE.Std_Logic_1164.ALL;

-- 實(shí)體聲明

Entity FreDevider is

port

(

Clock: IN Std_logic;

Clkout: OUT Std_logic

);

END;

-- 結(jié)構(gòu)體定義

Architecture Behavior Of FreDevider is

signal Clk:Std_Logic; -- 中間臨時(shí)變量

begin

process(Clock)--進(jìn)程

begin

IF rising_edge(Clock) THEN

Clk <= NOT Clk;

END IF;

END process;

Clkout <= Clk;

END

庫

常用的庫有IEEE庫、STD庫和WORK庫:

- IEEE庫:是VHDL設(shè)計(jì)中最常用的資源庫,包含IEEE標(biāo)準(zhǔn)的STD_LOGIC_1164、NUMERIC_BIT、NUMERIC_STD以及其他一些支持工業(yè)標(biāo)準(zhǔn)的程序包。其中最重要和最常用的是STD_LOGIC_1164程序包,大部分程序都是以此程序包中設(shè)定的標(biāo)準(zhǔn)為設(shè)計(jì)基礎(chǔ)。

- STD庫:是VHDL的標(biāo)準(zhǔn)庫,VHDL在編譯過程中會自動調(diào)用這個(gè)庫,所以使用時(shí)不需要用語句另外說明。

- WORK庫:是用戶在進(jìn)行VHDL設(shè)計(jì)時(shí)的現(xiàn)行工作庫,用戶的設(shè)計(jì)成果將自動保存在這個(gè)庫中,是用戶自己的倉庫,同STD庫一樣,使用該庫不需要任何說明。

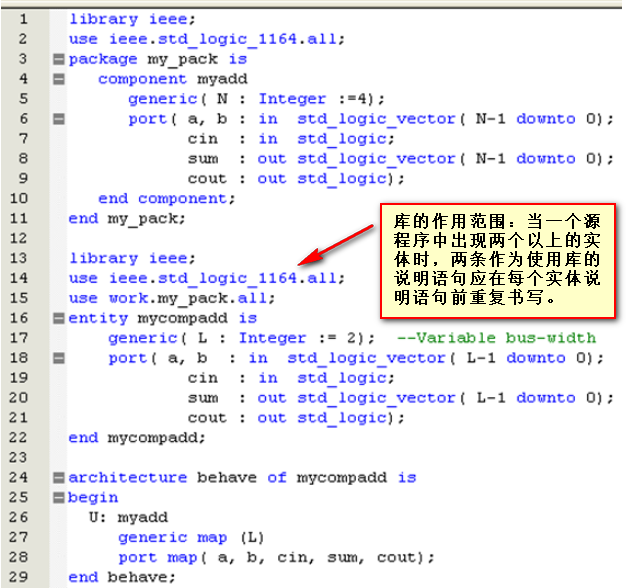

庫的作用范圍:

庫說明語句的作用范圍從一個(gè)實(shí)體說明開始到它所屬的構(gòu)造體、配置為止。當(dāng)一個(gè)源程序中出現(xiàn)兩個(gè)以上的實(shí)體時(shí),兩條作為使用庫的說明語句應(yīng)在每個(gè)實(shí)體說明語句前重復(fù)書寫。

?

程序包

--包頭

PACKAGE CHENGXUBAOMING IS

--程序包頭說明語句

END CHENGXUBAOMING;

--包體

PACKAGE BODY CHENGXUBAOMING IS

--程序包體說明語句

END CHENGXUBAOMING;

--調(diào)用程序包通用格式

USE 庫名.程序包名.ALL;

常用預(yù)定義程序包有以下四個(gè):

-

1.STD_LOGIC_1164程序包

STD_LOGIC_1164程序包定義了一些數(shù)據(jù)類型、子類型和函數(shù)。數(shù)據(jù)類型包括:STD_ULOGIC、STD_ULOGIC _VECTOR、STD_LOGIC和STD_LOGIC _VECTOR,用的最多最廣的是STD_LOGIC和STD_LOGIC_VECTOR數(shù)據(jù)類型。調(diào)用STD_LOGIC_1164程序包中的項(xiàng)目需要使用以下語句:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

該程序包預(yù)先在IEEE庫中編譯,是IEEE庫中最常用的標(biāo)準(zhǔn)程序包,其數(shù)據(jù)類型能夠滿足工業(yè)標(biāo)準(zhǔn),非常適合CPLD(或FPGA)器件的多值邏輯設(shè)計(jì)結(jié)構(gòu)。 -

2.STD_LOGIC_ARITH程序包

該程序包是美國Synopsys公司的程序包,預(yù)先編譯在IEEE庫中。主要是在STD_LOGIC_1164程序包的基礎(chǔ)上擴(kuò)展了UNSIGNED(無符號)、SIGNED(符號)和SMALL_INT(短整型)三個(gè)數(shù)據(jù)類型,并定義了相關(guān)的算術(shù)運(yùn)算符和轉(zhuǎn)換函數(shù)。 -

3.STD_LOGIC_SIGNED程序包

該程序包預(yù)先編譯在IEEE庫中,也是Synopsys公司的程序包。主要定義有符號數(shù)的運(yùn)算,重載后可用于INTEGER(整數(shù))、STD_LOGIC(標(biāo)準(zhǔn)邏輯位)和STD_LOGIC _VECTOR(標(biāo)準(zhǔn)邏輯位向量)之間的混合運(yùn)算,并且定義了STD_LOGIC _VECTOR到INTEGER的轉(zhuǎn)換函數(shù)。還定義了STD_LOGIC _VECTOR類型的符號數(shù)算數(shù)運(yùn)算子程序。 -

4.STD_LOGIC_UNSIGNED程序包

該程序包用來定義無符號數(shù)的運(yùn)算,其他功能與STD_LOGIC_SIGNED相似。

實(shí)體

ENTITY 實(shí)體名 IS -- 引導(dǎo)語句

[GENERIC (常數(shù)名: 數(shù)據(jù)類型: 設(shè)定值)] -- 類屬表

PORT -- 端口表

(

端口名1: 端口方向 端口類型;

端口名2: 端口方向 端口類型;

端口名3: 端口方向 端口類型;

......

端口名n: 端口方向 端口類型 -- 最后一個(gè)一定不能加";",不然會報(bào)next process的")" expect ";" or ","

);

END [實(shí)體名]; -- 結(jié)束語句

--port中端口默認(rèn)類型為signal

實(shí)體中--類屬

GENERIC (常數(shù)名:數(shù)據(jù)類型:設(shè)定值); --類似于C中的宏定義

--放在實(shí)體或者塊結(jié)構(gòu)體前面的說明部分

--舉例

ENTITY mcu1 IS

GENERIC (addrwidth : INTEGER := 16);

PORT(

add_bus : OUT STD_LOGIC_VECTOR(addrwidth-1 DOWNTO 0) );

...

實(shí)體中--端口

PORT(端口信號名:端口模式 數(shù)據(jù)類型;

端口信號名:端口模式 數(shù)據(jù)類型);

- 端口模式有:

- IN : 在實(shí)體中只讀,接受外來數(shù)據(jù). 只能出現(xiàn)在賦值語句的右側(cè)。

- OUT: 在實(shí)體中只能更新,不可讀。只能出現(xiàn)在賦值語句的左側(cè)。

- INOUT: 在實(shí)體內(nèi)部可更新、可讀,可出現(xiàn)在賦值語句的兩側(cè)。

- BUFFER: 可用作內(nèi)部賦值,可出現(xiàn)在賦值語句的兩側(cè)。在可綜合代碼中不推薦使用。

結(jié)構(gòu)體(并發(fā))

- 用于描述模型的功能

- 必須和一個(gè) Entity相關(guān)聯(lián)

- 一個(gè)Entity可有多個(gè) Architectures

- Architecture 語句并發(fā)執(zhí)行.

Architecture 結(jié)構(gòu)體名 OF 實(shí)體名 IS

定義語句法;

BEGIN

功能描述語句法;

END 結(jié)構(gòu)體名稱;

- 結(jié)構(gòu)描述(接近原理圖)

- 數(shù)據(jù)流描述(并發(fā)代碼)

- 行為描述(順序、并發(fā))

結(jié)構(gòu)  數(shù)據(jù)流

數(shù)據(jù)流

行為

--兩位相等比較器

entity equ2 is

port(a,b:in std_logic_vector(1 downto 0);

equ:out std_logic);

end equ2;

--結(jié)構(gòu)體結(jié)構(gòu)描述:用元件例化,即網(wǎng)表形式來實(shí)現(xiàn);

architecture netlist of equ2 is

-- nor 或非component nor2

port(a,b :in std_logic;

c :out std_logic);

end component;

component xor2-- xor 異或

port(a,b :in std_logic;

c :out std_logic);

end component;

signal x: std_logic_vector(1 downto 0);

begin

U1:xor2 port map(a(0),b(0),x(0));

U2:xor2 port map(a(1),b(1),x(1));

U3:nor2 port map(x(0),x(1),equ);

end netlist;

--結(jié)構(gòu)體數(shù)據(jù)流描述:用布爾方程來實(shí)現(xiàn):

architecture equation of equ2 is

begin

equ<=(a(0) xor b(0)) nor(a(1) xor b(1));

end equation;

--結(jié)構(gòu)體行為描述:用順序語句來實(shí)現(xiàn):

architecture con_behave of equ2 is

begin

process(a,b)

begin

if a=b then

equ<='1';

else

equ<='0';

end if;

end procerss;

end con_behave;

--結(jié)構(gòu)體行為描述:用并行語句來實(shí)現(xiàn):

architecture seq_behave of equ2 is

begin

equ<='1' when a=b else '0';

end sqq_behave;

塊語句

塊結(jié)構(gòu)名: BLOCK

端口說明 類屬說明

BEGIN

并行語句

END BLOCK 塊結(jié)構(gòu)名;

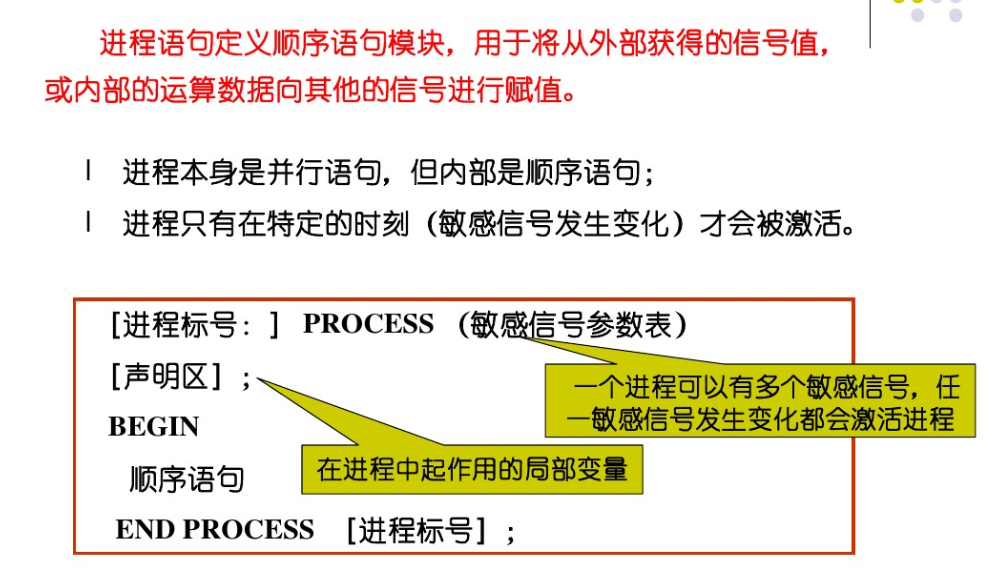

進(jìn)程語句

進(jìn)程名: PROCESS(敏感信號表) IS

進(jìn)程說明

BEGIN

順序描述語句

END PROCESS 進(jìn)程名; --進(jìn)程名字可省略

配置Configuration

- 用于實(shí)現(xiàn)模型的關(guān)聯(lián),可將一個(gè) Entity 和一個(gè)Architecture關(guān)聯(lián)起來,也可將一個(gè) component 和一個(gè) entity-architecture關(guān)聯(lián)起來。

- 目的是為了在一個(gè)實(shí)體中靈活的使用不同的Architecture。可以在仿真環(huán)境中大量使用,但是在綜合環(huán)境中限制使用。

Configuration 配置名 of 實(shí)體名 IS

for 結(jié)構(gòu)體名

end for;

end Configuration;

子程序

能被主程序反復(fù)調(diào)用并能將處理結(jié)果傳送到主程序的程序模塊,子程序分為過程語句(Procedure)和函數(shù)(Functure)兩種。子程序中的參數(shù)說明是局部的,只能在子程序體內(nèi)起作用。

子程序--過程Procedure

PROCEDURE 過程名(參數(shù)1;參數(shù)2;——) IS

定義語句;

BEGIN

順序處理語句;

END 過程名;

子程序--函數(shù)Function

FUNCTION 函數(shù)名(參數(shù)1;參數(shù)2;——)

RETURN 數(shù)據(jù)類型 IS

定義語句;

BEGIN

順序處理語句;

RETURN 返回變量名;

學(xué)習(xí)基本語法

標(biāo)識符

標(biāo)識符用來定義常數(shù)、變量、信號、端口、子程序或者參數(shù)的名字

- 首字符必須是字母

- 末字符不能為下劃線

- 不允許出現(xiàn)兩個(gè)連續(xù)的下劃線

- 不區(qū)分大小寫

- VHDL定義的保留字(關(guān)鍵字),不能用作標(biāo)識符

- 標(biāo)識符字符最長可以是32個(gè)字符

- 注釋由兩個(gè)連續(xù)的下劃線(--)引導(dǎo)

關(guān)鍵字(不能作為標(biāo)識符)

數(shù)據(jù)對象

- 信號SIGNAL

- 變量VARIABLE

- 常量CONSTAT

--舉例信號

SIGNAL brdy: BIT;

SIGNAL output : INTEGER:=2;

目標(biāo)信號名<=表達(dá)式

--為全局變量,在程序包說明、實(shí)體說明、結(jié)構(gòu)體描述中使用,用于聲明內(nèi)部信號,而非外部信號(外部信號為IN、OUT、INOUT、BUFFER),其在元件之間起互聯(lián)作用,可以賦值給外部信號。

--舉例變量

VARIABLE opcode:BIT_VECTOR(3 downto 0):= "0000";

VARIABLE freq: INNTEGER;

變量賦值符號":=",變量賦值立刻更新。

--只在給定的進(jìn)程(process)中用于聲明局部值或用于子程序中,變量的賦值符號為“:=”,和信號不同,信號是實(shí)際的,是內(nèi)部的一個(gè)存儲元件(SIGNAL)或者是外部輸入(IN、OUT、INOUT、BUFFER),而變量是虛的,僅是為了書寫方便而引入的一個(gè)名稱,常用在實(shí)現(xiàn)某種算法的賦值語句當(dāng)中。

--常量舉例

CONSTANT rise_fall_time: TIME:=2ns;

CONSTANT data_bus: INTEGER:=16;

--在結(jié)構(gòu)體描述、程序包說明、實(shí)體說明、過程說明、函數(shù)調(diào)用說明和進(jìn)程說明中使用,在設(shè)計(jì)中描述某一規(guī)定類型的特定值不變,如利用它可設(shè)計(jì)不同模值的計(jì)數(shù)器,模值存于一常量中,對不同的設(shè)計(jì),改變模值僅需改變此常量即可,就如參數(shù)化元件。

數(shù)據(jù)類型

VHDL常用的數(shù)據(jù)類型有三種:

- 標(biāo)準(zhǔn)定義的數(shù)據(jù)類型

- IEEE預(yù)定義標(biāo)準(zhǔn)邏輯位

- 矢量及用戶自定義的數(shù)據(jù)類型。

- 布爾(Boolean): 取值為FALSE和TRUE,不是數(shù)值,不能運(yùn)算,一般用于關(guān)系運(yùn)算符

- 位(Bit): 取值為0和1,用于邏輯運(yùn)算

- 字符(character): 通常用''引號引起來,區(qū)分大小寫

- 字符串(String): 通常用""雙引號引起來,區(qū)分大小寫

- 整數(shù)(Integer):

- 實(shí)數(shù)(real): 實(shí)數(shù)類型僅能在VHDL仿真器中使用,綜合器不支持

- 時(shí)間(Time) : 物理量數(shù)據(jù),包括整數(shù)和單位兩個(gè)部分 表達(dá)方法包含數(shù)字、(空格)單位兩部分,如(10 PS) 常用單位:fs,ps,ns,us,ms,sec,min,hr

- 錯(cuò)誤等級(severity level): 表示系統(tǒng)狀態(tài)

Type BOOLEAN IS (FALSE,TRUE);

TYPE BIT IS('0','1');

TYPE BIT_VECTOR IS ARRAY(Natural range<>)OF BIT;

SIGNAL a:BIT_VECTOR(0 TO 7);

TYPE CHARACTER IS (NUL,SOH,STX,'','!');

VARIABLE string_var:STING(1 TO 7);

string_var:="abcd";

VARIABLE a:INTEGER -63 to 63

(1)整數(shù)(INTEGER) 范圍:-2147483547~+2147483646,即可用 32位有符號的二進(jìn)制數(shù)表示。如2、10E4、16#D2#。

例:INTEGER RANGE 100 DOWNTO 0

(2)實(shí)數(shù)(REAL) 范圍:-1.0E38~1.0E38,書寫時(shí)一定要有小數(shù)。 如: 65.36、 8#43.6#E+4。

(3) 位(BIT) 取值只能是用帶單引號的‘1’和‘0’來表示。

(4)位矢量(BIT_VECTOR)位矢量是用雙引號括起來的一組位數(shù)據(jù),如“010101”。例:SIGNAL A2:BIT_ VECTOR (3 DOWNTO 0);

(5)布爾量(BOOLEAN) 只有“真”和“假”2個(gè)狀態(tài),可以進(jìn)行關(guān)系運(yùn)算。

(6)字符(CHARACTER):字符通常用單引號括起來,對大小寫敏感。

(7)字符串(STRING):字符串是雙引號括起來的一串字符,如“l(fā)aksdklakld”。

(8)時(shí)間(TIME):完整的時(shí)間類型包括整數(shù)和物理量單位兩部分,整數(shù)和單位之間至少留一個(gè)空格,如55 ms,20 ns。

(9)自然數(shù)(NATURAL)和正整數(shù)(POSITIVE)數(shù)據(jù)類型

自然數(shù)是整數(shù)的一個(gè)子類型,非負(fù)的整數(shù),即零和正整數(shù)。

正整數(shù)也是整數(shù)的一個(gè)子類型,它包括整數(shù)中非零和非負(fù)的數(shù)值。

(10)錯(cuò)誤等級(SEVERITY LEVEL)

在 VHDL 仿真器中, 錯(cuò)誤等級用來指示設(shè)計(jì)系統(tǒng)的 工作狀態(tài),共有四種可能的狀態(tài)值,

即 NOTE(注意)、WARNING(警告)、ERROR(出錯(cuò))、FAILURE(失敗)。

(11)綜合器不支持的數(shù)據(jù)類型

物理類型。綜合器不支持物理類型的數(shù)據(jù),如具有量綱型的數(shù)據(jù),包括時(shí)間類型,這些類型只能用于仿真過程。

浮點(diǎn)型。如 REAL 型。

Aceess型。綜合器不支持存取型結(jié)構(gòu),因?yàn)椴淮嬖谶@樣對應(yīng)的硬件結(jié)構(gòu)。

File 型。綜合器不支持磁盤文件型,硬件對應(yīng)的文件僅為 RAM 和 ROM。

(12)其他預(yù)定義數(shù)據(jù)類型

VHDL 綜合工具配帶的擴(kuò)展程序包中,定義了一些有用的類型,如 Synopsys 公司在IEEE 庫中加入的程序包 STD_LOGIC_ARITH 中定義了如下的數(shù)據(jù)類型:無符號型(UNSIGNED)、 有符號型(SIGNED)和小整型(SMALL_INT)。

標(biāo)準(zhǔn)邏輯位(STD_LOGIC)數(shù)據(jù)類型

TYPE STD_LOGIC IS (‘U’,‘X’,‘0’,‘1’,‘Z’,‘W’,‘L’,‘H’,‘-’);

各值的含義是:

‘U’--未初始化的,

‘X’--強(qiáng)未知的,

'0'--強(qiáng)0,'1'--強(qiáng)1,

'Z'--高阻態(tài),

'W'--弱未知的,

'L'--弱0,'H'--弱1,

'-'--忽略。

在程序中使用此數(shù)據(jù)類型前,需加入下面的語句:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

標(biāo)準(zhǔn)邏輯矢量(STD_LOGIC_VECTOR)數(shù)據(jù)類型

STD_LOGIC_VECTOR類型定義如下:

TYPE STD_LOGIC_VECTOR IS ARRAY (NATURAL RANGE<>) OF STD_LOGIC;

顯然,STD_LOGIC_VECTOR是定義在STD_LOGIC_1164程序包中的標(biāo)準(zhǔn)一維數(shù)組,數(shù)組中的每一個(gè)元素的數(shù)據(jù)類型都是以上定義的標(biāo)準(zhǔn)邏輯位STD_LOGIC。

用戶自定義數(shù)據(jù)類型

VHDL允許用戶自行定義新的數(shù)據(jù)類型,如枚舉類型(ENUMERATION TYPE)、整數(shù)類型(INTEGER TYPE)、數(shù)組類型(ARRAY TYPE)、記錄類型(RECORD TYPE)、時(shí)間類型(TIME TYPE)、實(shí)數(shù)類型(REAL TYPE)等。用戶自定義數(shù)據(jù)類型是用類型定義語句TYPE和子類型定義語句SUBTYPE實(shí)現(xiàn)的。

用戶自定義數(shù)據(jù)類型的一般格式:

TYPE 數(shù)據(jù)類型名 IS 數(shù)據(jù)類型定義 [OF 基本數(shù)據(jù)類型];

TYPE digit IS INTEGER RANGE 0 TO 9;

TYPE current IS REAL RANGE -1E4 TO 1E4;

TYPE word IS ARRAY (INTEGER 1 TO 8) OF STD_LOGIC;

(關(guān)鍵詞OF后的基本數(shù)據(jù)類型是指數(shù)據(jù)類型定義中所定義的元素的基本數(shù)據(jù)類型,一般都是取已有的預(yù)定義數(shù)據(jù)類型,如BIT、STD_LOGIC或INTEGER等。)

(TO是BIT和STD_LOGIC之間的轉(zhuǎn)化)

(CONV是STD_LOGIC、SIGNED、INTEGER之間的轉(zhuǎn)化)

運(yùn)算符

算術(shù)運(yùn)算符

- +,-,*,/

- MOD取模

- REM取余

- SLL 邏輯左移

- SRL 邏輯右移

- SLA 算數(shù)左移

- SRA 算數(shù)右移

- ROL 循環(huán)左移

- ROR 循環(huán)右移

- ** 乘方

- ABS() :絕對值

關(guān)系運(yùn)算符

-

=

-

/=

-

<

-

<=

-

. >=

邏輯運(yùn)算符

- AND

- OR

- NAND

- NOR

- NOT

- XNOR

- XOR

賦值運(yùn)算符

- <= 信號賦值(最后賦值)

- := 邏輯賦值(即時(shí)賦值)

關(guān)聯(lián)運(yùn)算符

- =>

其他運(yùn)算符

-

-

- & 并置運(yùn)算符

運(yùn)算符優(yōu)先級

VHDL基本語句

并行語句

- 每一并行語句內(nèi)部的語句運(yùn)行方式可以有兩種不同的方式,即并行執(zhí)行方式(如塊語句)和順序執(zhí)行方式(如進(jìn)程語句)。因此,VHDL并行語句勾畫出了一幅充分表達(dá)硬件電路的真實(shí)的運(yùn)行圖景。

ARCHITECTURE NAME OF NAME2 IS

說明語句;

BEGIN

并行語句;

END ARCHITECTURE NAME;

- 并行信號賦值語句(CONCURRENT SIGNAL ASSIGNMENTS)

- 條件/選擇信號賦值語句(CONDITIONAL/SELECTED SIGNAL ASSIGNMENTS)

- 進(jìn)程語句(PROCESS STATEMENTS)

- 塊語句(BLOCK STATEMENTS)

- 元件例化語句(COMPONENT INSTANTIATIONS)

- 生成語句(GENERATE STATEMENTS)

- 并行過程調(diào)用語句(CONCURRENT PROCEDURE CALLS)

并行信號賦值語句

<signal_name> <= <expression>;

Example:

q <= input1 or input2;

q <= input1 and input2;

-- 最終執(zhí)行 q <= input1 and input2;

條件信號賦值語句

SIGNAL_NAME <= <SIGNAL/VALUE> WHEN <CONDITION1> else

<SIGNAL/VALUE> WHEN <CONDITION2> else

<SIGNAL/VALUE> WHEN <CONDITION3> else

<SIGNAL/VALUE> WHEN <CONDITION4> else

<SIGNAL/VALUE> WHEN <CONDITION5> else

……

<SIGNAL/VALUE> WHEN <CONDITIONN> else

<SIGNAL/VALUE> ;

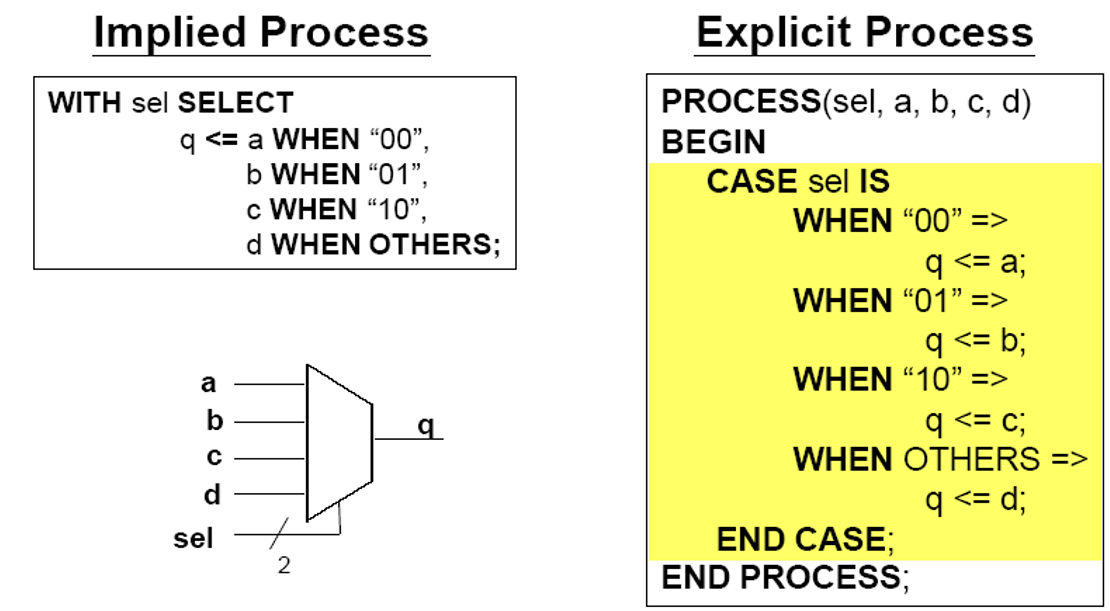

選擇信號賦值語句

WITH <EXPRESSION> SELECT

<SIGNAL_NAME> <= <SIGNAL/VALUE> WHEN <CONDITION1>,

<SIGNAL/VALUE> WHEN <CONDITION2>,

<SIGNAL/VALUE> WHEN OTHERS;

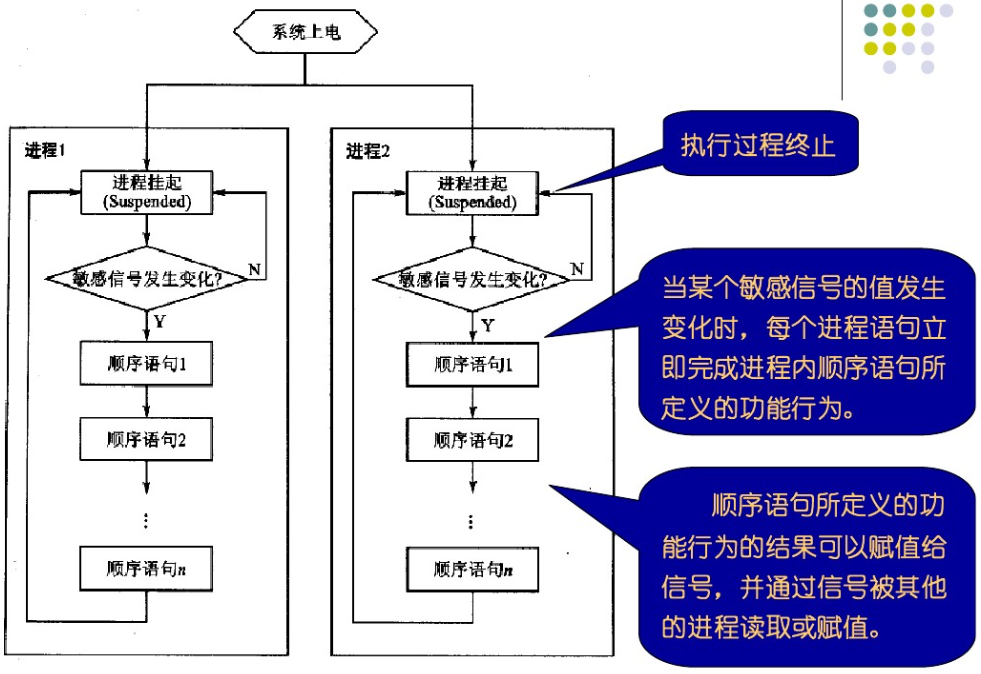

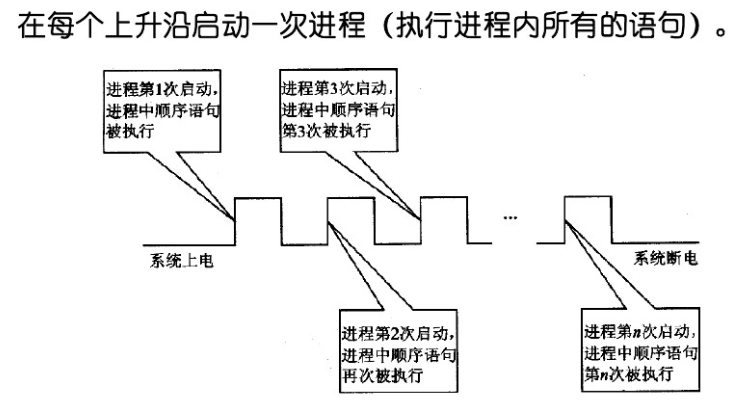

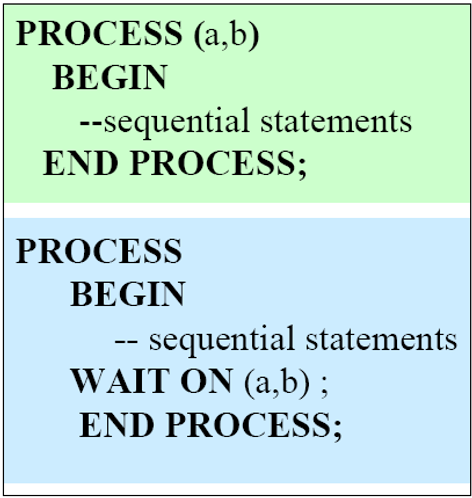

進(jìn)程語句

從本質(zhì)上講VHDL的所有語句都是并行語句。進(jìn)程(process)語句是用來給并行的硬件提供順序語句,一個(gè)結(jié)構(gòu)體可以包含多個(gè)進(jìn)程,多個(gè)進(jìn)程之間并行運(yùn)行。進(jìn)程內(nèi)部的語句順序執(zhí)行。

--上升沿描述

Clock'EVENT AND Clock='1'

--下降沿描述

Clock'EVENT AND Clock='0'

--上升沿描述

rising_edge(Clock)

--下降沿描述

falling_edge(Clock)

敏感表和wait語句

- 敏感表和WAIT語句等效,但是WAIT語句更多樣化

- 一個(gè)進(jìn)程不可既有敏感表又有WAIT語句,但是要有一種

- 邏輯綜合對WAIT有嚴(yán)格的限制(只有WAIT UNTILL語句可以綜合)

WAIT UNTIL CONDITION;

--舉例說明

architecture arc2 of process_wait is

begin

process

begin

wait until clk'event and clk = '1';

q<=d;

end process;

end architecture;

WAIT ON SENSITIVITY LIST;

WAIT ON (A,B,C);--敏感表,任意一個(gè)發(fā)生變化才會執(zhí)行

- 進(jìn)程內(nèi)部,對同一信號多次賦值,只最后一次起作用,即最靠近end process;的

process(a,b,s)

begin

--final results: s<=a+b y<=a+b+1

y<=s+1;

s<=a;

s<=a+b;

end process;

- 進(jìn)程內(nèi)部,對同一變量多次賦值,立即執(zhí)行。

process(a,b)

variable ss: std_logic_vector(3 downto 0);

begin

ss:=a;

y<=ss+1;

ss:=a+b;

end process;

--結(jié)果:由于y<=ss+1寫在ss:=a之后,所以將a+1的值賦給y

塊語句

塊(BLOCK)語句是一種將結(jié)構(gòu)體中的并行描述語句進(jìn)行組合的方法,它的主要目的是改善并行語句及其結(jié)構(gòu)的可讀性,或是利用BLOCK的保護(hù)表達(dá)式關(guān)閉某些信號。

塊標(biāo)號:BLOCK [(塊保護(hù)表達(dá)式)] [IS]

接口說明;

類屬說明;

BEGIN

并行語句;

END BLOCK [塊標(biāo)號];

元件例化語句

-

元件例化就是將預(yù)先設(shè)計(jì)號的設(shè)計(jì)實(shí)體定義為一個(gè)元件,然后利用特定的語句將此元件與當(dāng)前的設(shè)計(jì)實(shí)體中的指定端口相連接,從而為當(dāng)前設(shè)計(jì)實(shí)體引入一個(gè)新的低一級的設(shè)計(jì)層次

-

元件例化語句由兩部分組成前一部分是將一個(gè)現(xiàn)成的設(shè)計(jì)實(shí)體定義為一個(gè)元件的語句,第二部分則是此元件與當(dāng)前設(shè)計(jì)實(shí)體中的連接說明。

-

COMPONENT 元件名 IS [GENERIC(類屬表)說明;] [PORT(端口名表)說明;] END COMPONENT 元件名;

生成語句

- 生成語句作用:復(fù)制

- 根據(jù)某些條件設(shè)置好某一原件或設(shè)計(jì)單位,可以用生成語句復(fù)制一組完全相同的并行元件或設(shè)計(jì)單元電路

[標(biāo)號:] FOR 循環(huán)變量 IN 取值范圍 GENERATE

[說明部分]

并行語句;

END GENERATE [標(biāo)號];

--取值范圍: 表達(dá)式 to 表達(dá)式 或者 表達(dá)式 downto 表達(dá)式

并行過程調(diào)用語句

- 并行過程調(diào)用語句作為并行語句直接出現(xiàn)在結(jié)構(gòu)體中0

- 調(diào)用語句可以為:過程(Procedure)或者函數(shù)(Function)

- 調(diào)用的語法格式:過程名/函數(shù)名(關(guān)聯(lián)參數(shù)表)

- 函數(shù)和過程統(tǒng)稱子函數(shù)子程序

過程

-

- 參數(shù)可以是 in, out, inout 模式

- 輸入?yún)?shù)(in)的默認(rèn)數(shù)據(jù)類型是constant

- 輸出參數(shù)(out)或者inout參數(shù)默認(rèn)數(shù)據(jù)類型variable

- 參數(shù)對象可為 constant, variable and signal

- 過程調(diào)用參數(shù)需要一一對應(yīng),形參為constant, 實(shí)參可以為signal、constant或variable;形參若 為signal或variable,則實(shí)參需對應(yīng)一致的類型

- 參數(shù)可以是 in, out, inout 模式

-

- 其特征是過程中可以修改參數(shù)值(out,inout模式 參數(shù))

- 不需要RETURN語句

PROCEDURE NAME IS

[聲明部分]

BEGIN

順序語句;

END PROCEDURE NAME;

函數(shù) --函數(shù)一般定義在包中(聲明及實(shí)現(xiàn))

- 產(chǎn)生一個(gè)返回值。

- 參數(shù)只能為in模式。

- 傳遞的參數(shù)在函數(shù)內(nèi)部只能使用不能修改(因?yàn)閰?shù)為in)。

- 允許的參數(shù)數(shù)據(jù)類型為 constant或signal,默認(rèn)constant。

- 形參和實(shí)參必須匹配。形參為constant,則實(shí)參可以是variable、signal、 constant或表達(dá)式;形參為signal,實(shí)參要為 signal。

- 需要一個(gè)RETURN 語句 。

FUNCTION NAME

RETURN data_type IS

[聲明部分];

BEGIN

順序語句;

RETURN 聲明名;

END FUNCTION NAME;

--函數(shù)一般定義在包中(聲明及實(shí)現(xiàn))

過程與函數(shù)的區(qū)別:

- 函數(shù)參數(shù)只能使用IN。過程中參數(shù)為IN、 INOUT、OUT三種。

- 函數(shù)只有一個(gè)返回值。過程可以通過參數(shù)返回 多個(gè)返回值。

順序語句

- 順序信號/變量賦值語句

- IF-THEN語句

- CASE語句

- LOOP語句

- RETURN語句

- NULL語句

順序信號/變量賦值語句

進(jìn)程中的順序信號賦值語句

signal<=expression;

END PROCESS時(shí)更新

多次賦值,以最后一次賦值為準(zhǔn)

進(jìn)程中的順序變量賦值語句

variable:=expression;

立刻更新

多次賦值,以最后一次賦值為準(zhǔn)

IF-THEN語句

IF A='1' THEN

B<=1;

ELSEIF A='2' THEN

B<=2;

……

ELSE

B<=255;

END IF;

--順序從上到下,有優(yōu)先級

--可以嵌套

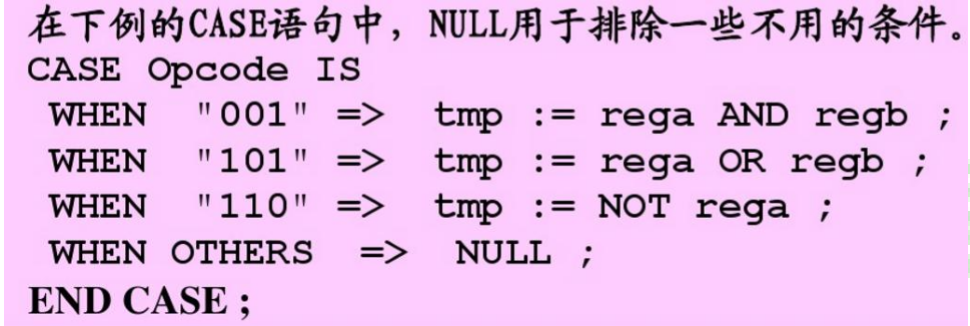

CASE語句

CASE A IS

WHEN '1'=> B<=1;

WHEN '2'=> B<=2;

……

WHEN OTHERS=> B<=255;

END CASE;

- 條件只杯評估一次

- 沒有優(yōu)先級必須包括所有的條件(可以沒有WHEN OTHERS,但是必須包括所有條件)

- WHEN OTHERS語句包括了沒有指定的所有條件

LOOP語句

1.無限LOOP,LOOP將會無限執(zhí)行,除非EXIT語句存在

NAME LOOP

---

EXIT NAME;

END LOOP;

2.WHILE LOOP。條件滿足則循環(huán)

WHILE CONDITION LOOP

----

END LOOP;

3.FOR LOOP.迭代LOOP

FOR <IDENTIFIER> IN <RANGE> LOOP

-----

END LOOP;

示例

--四位左移

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SHIFT4 IS

PORT(

SHFT_LFT:IN STD_LOGIC;--允許位

D_IN: IN STD_LOGIC_VECTOR(3 DOWNTO 0);--輸入4位

Q_OUT: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--輸出8位

);

END SHIFT4;

ARCHITECTURE LOGIC OF SHIFT4 IS

BEGIN

PROCESS(D_IN,SHFT_LFT)

VARIABLE SHFT_VAR:STD_LOGIC_VECTOR(7 DOWNTO 0);--進(jìn)程說明語句部分定義變量

BEGIN

SHFT_VAR(7 DOWNTO 4):="0000";--變量上4位為0

SHFT_VAR(3 DOWNTO 0):=D_IN; --變量下4位為輸入

IF SHFT_LFT='1'THEN--如果允許

FOR I IN 7 DOWNTO 4 LOOP--下4位被搬移到上4位

SHFT_VAR(I):=SHFT_VAR(I-4);

END LOOP;

SHFT_VAR(3 DOWNTO 0):="0000";--下4位歸0

ELSE

SHFT_VAR:=SHFT_VAR;--如果不被允許,不搬移,輸入在下4位

END IF;

Q_OUT<=SHFT_VAR;--變量被搬移到輸出

END PROCESS;

END LOGIC;

RETURN語句

RETURN語句是一段子程序結(jié)束后,返回主程序的語句

RETURN;--只能用于過程,它后面不要有表達(dá)式

RETURN 表達(dá)式;--只用于函數(shù),它后面必須有表達(dá)式,函數(shù)結(jié)束必須用RETURN語句

示例

--過程

PROCEDURE RE(SIGNAL S,R:IN STD_LOGIC

SIGNAL Q:INOUT STD_LOGIC) IS

BEGIN

IF(S='1'andr='1')THEN

REPORT"FORBIDDEN STATE:S AND R ARE QUUAL TO '1'";

RETURN;

ELSE

Q <= S AND R AFTER 5NS;

END IF;

END PROCEDURE RS;

--函數(shù)

FUNCTION OPT(A,B,OPR:STD_LOGIC) RETURN STD_LOGIC IS

BEGIN

IF(OPR='1')THEN RETURN (A AND B);

ELSE RETURN (A OR B);

END IF;

END FUNCTION OPT;

NULL語句

空操作

NULL;

代碼

二輸入與非門

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY demo4 IS

PORT (a,b: IN STD_LOGIC;

y: OUT STD_LOGIC);

END demo4;

ARCHITECTURE NAND2PP OF demo4 IS

BEGIN

y<= a NAND b;

END NAND2PP;

二輸入或非門

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY demo5 IS

PORT(a,b: IN STD_LOGIC;

y: OUT STD_LOGIC);

END demo5;

ARCHITECTURE HUOFEIMEN OF demo5 IS

BEGIN

y <= a NOR b;

END HUOFEIMEN;

各個(gè)門

--同時(shí)實(shí)現(xiàn)一個(gè)與門、或門、與非門、或非門、異或門及反相器的邏輯

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY demo6 IS

PORT(

a,b: IN STD_LOGIC;

YAND,YOR,YNAND,YNOR,YXOR,YN: OUT STD_LOGIC

);

END demo6;

ARCHITECTURE LUAN OF demo6 IS

BEGIN

YAND <= a AND b;

YNAND <= a NAND b;

YOR <= a OR b;

YNOR <= a NOR b;

YXOR <= a XOR b;

YN <= NOT a;

END LUAN;

3-8譯碼器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY demo7 IS

PORT

(

A,B,C: IN STD_LOGIC;

Y : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END demo7;

ARCHITECTURE KEWU OF demo7 IS

SIGNAL ABC: STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

ABC <= A&B&C;

PROCESS(ABC)

BEGIN

CASE ABC IS

WHEN "000"=>Y<="11111110";

WHEN "001"=>Y<="11111101";

WHEN "010"=>Y<="11111011";

WHEN "011"=>Y<="11110111";

WHEN "100"=>Y<="11101111";

WHEN "101"=>Y<="11011111";

WHEN "110"=>Y<="10111111";

WHEN "111"=>Y<="01111111";

WHEN OTHERS=>Y<="XXXXXXXX";

END CASE;

END PROCESS;

END KEWU;

3-8譯碼器(類型轉(zhuǎn)化解決式)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164,ALL;

USE IEEE.STD_LOGIC_UNSIGNED,ALL;

ENTITY DECODER3TO8 IS

PORT(

INPUT: IN STD_LOGIC_VECTOR(2 DOWNTO 0);

OUTPUT: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END DECODER3TO8;

ARCHITECTURE BEHAVE OF DECODER3TO8 IS

BEGIN

PROCESS(INPUT)

BEGIN

OUTPUT<=(OTHERS=>'0');

OUTPUT(CONV_INTEGER(INPUT))<='1';

END PROCESS;

END BEHAVE;

--在STD_LOGIC_UNSIGNED中,CONV_INTEGER()是把STD_LOGIC轉(zhuǎn)換成INTEGER

--在STD_LOGIC_ARITH中, CONV_INTEGER()是把UNSIGNED,SIGNED轉(zhuǎn)換成INTEGER

--例如,假設(shè)INPUT是010,直接轉(zhuǎn)化成了INTEGER數(shù)字2

異步復(fù)位(清零)

PROCESS(CLK,RESET,A)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

Q <=A+1;

ELSIF RESET='1' THEN

Q <='0';

END IF

END PROCESS;

同步復(fù)位(清零)

PROCESS(CJK,RESET,A)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF RESET='1' THEN

Q <= '0';

ELSE

Q <=A+1;

END IF;

END IF;

END PROCESS;

使用異步RESET的8BIT寄存器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY REG8 IS

PORT(

D: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

RESETN,CLOCK: IN STD_LOGIC;

Q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END REG8;

ARCHITECTURE BEHAVIORAL OF REG8 IS

BEGIN

PROCESS(RESETN,CLOCK)

BEGIN

IF(RESETN='0') THEN

Q <="00000000";

ELSIF (CLOCK'EVENT AND CLOCK='1') THEN

Q <= D;

END IF;

END PROCESS;

END BEHAVIORAL;

使用異步清零的NBIT寄存器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY REGN IS

GENERIC (N:INTEGER:=16);

PORT(

D: IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

RESET,CLOCK: IN STD_LOGIC;

Q: OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0);

);

ARCHITECTURE BEHAVIORAL OF REGN IS

BEGIN

PROCESS(RESET,CLOCK)

BEGIN

IF(RESET='0') THEN

Q <= (OTEHRS => '0'); --給Q的所有位賦0,方便用于多位信號的賦值操作

ELSIF (CLOCK'EVENT AND CLOCK='1') THEN

Q <= D;

END IF;

END PROCESS;

END BEHAVIORAL;

計(jì)數(shù)器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSGNED.ALL;

ENTITY COUNT_A IS

PORT(

CLK,RST.UPDN: IN STD_LOGIC;

Q: OUT STD_LOGIC_VECTOR(15 DOWNTO 0)

);

END COUNT_A;

ARCHITECTURE LOGIC OF COUNT_A IS

BEGIN

PROCESS(RESET,CLOCK)

VARIABLE TMP_Q:STD_LOGIC_VECTOR(15 DOWNTO 0);

BEGIN

IF(RST='0') THEN

Q<=(OTHERS=>'0');--異步復(fù)位

ELSIF(CLOCK'EVENT AND CLOCK='1')

IF UPDN='1'THEN

TMP_Q:=TMP_Q+1;

ELSE

TMP_Q=TMP_Q-1;

END IF;

Q<=TMP_Q;

END IF;

END PROCESS;

END LOGIC;

4BIT帶進(jìn)位全加器(行為描述)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY ADDER4_FULL IS

PORT(

A: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

B: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

CI: IN STD_LOGIC;

S: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CO: OUT STD_LOGIC

);

END ADDER4_FULL;

ARCHITECTURE RTL OF ADDER4_FULL IS

BEGIN

PROCESS(A,B,CI)

VARIABLE A_T,B_T,C_T,S_T: STD_LOGIC_VECTOR(4 DOWNTO 0);

BEGIN

-- &拼接符

A_T :='0'&A;

B_T :='0'&B;

C_T :="0000"&CI;

S_T :=A_T+B_T+C_T;

CO<=S_T(4);

S <=S_T(3 DOWNTO 0);

END PROCESS;

END RTL;

四選一電路

-----------以下是錯(cuò)誤代碼-----------------

-----------以下是錯(cuò)誤代碼-----------------

-----------以下是錯(cuò)誤代碼-----------------

-----------以下是錯(cuò)誤代碼-----------------

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DEMO1 IS

PORT(

INPUT: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

SW: IN STD_LOGIC_VECTOR(1 DOWNTO 0);

OUTPUT: OUT STD_LOGIC

);

END DEMO1;

ARCHITECTURE BEHAVE OF DEMO1 IS

BEGIN

PROCESS(INPUT,SW)------------------這句應(yīng)當(dāng)去掉

BEGIN

OUTPUT<=INPUT(3)WHEN SW="11" ELSE

INPUT(2)WHEN SW="10" ELSE

INPUT(1)WHEN SW="01" ELSE

INPUT(0)WHEN SW="00" ELSE

'0';

END PROCESS;-----------------------這句應(yīng)當(dāng)去掉

END BEHAVE;

-----------以上是錯(cuò)誤代碼-----------------

-----------以上是錯(cuò)誤代碼-----------------

-----------以上是錯(cuò)誤代碼-----------------

-----------以上是錯(cuò)誤代碼-----------------

--因?yàn)?在VHDL中,IF...THEN...ELSE是順序語句,只能出現(xiàn)在行為描述中(進(jìn)程體或者子程序中);而WHEN...ELSE是并行語句,可以直接出現(xiàn)在結(jié)構(gòu)體中,但卻不能出現(xiàn)在行為描述中。WHEN...ELSE等效于一個(gè)進(jìn)程體為IF...THEN...ELSE語句的進(jìn)程。

四選一電路(CASE)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DEMO1 IS

PORT(

INPUT: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

SW: IN STD_LOGIC_VECTOR(1 DOWNTO 0);

OUTPUT: OUT STD_LOGIC

);

END DEMO1;

ARCHITECTURE BEHAVE OF DEMO1 IS

BEGIN

PROCESS(INPUT,SW)

BEGIN

CASE SW IS

WHEN "00" => OUTPUT<=INPUT(0);

WHEN "01" => OUTPUT<=INPUT(1);

WHEN "10" => OUTPUT<=INPUT(2);

WHEN "11" => OUTPUT<=INPUT(3);

WHEN OTHERS=>OUTPUT<='X';--x是強(qiáng)未知,這句話是必須的,因?yàn)镾TD_LOGIC的類型很多

END CASE;

END PROCESS;

END BEHAVE;

二選一電路(IF)

IF (P1='1') THEN----p1p2:"10""11"

Z<=A;

ELSIF (P2='1') THEN----p1p2:"01"

Z<=B;

ELSE----p1p2:"00"

Z<=C;

奇偶校驗(yàn)電路(LOOP)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DEMO1 IF

PORT(

INPUT: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

OUTPUT: OUT STD_LOGIC

);

END DEMO1;

ARCHITECTURE BEHAVE OF DEMO1 IS

VARIABLE X:STD_LOGIC;

BEGIN

PROCESS(INPUT)

BEGIN

X:='0';

FOR I IN 7 DOWNTO 0 LOOP

X:=X XOR INPUT(I);

END LOOP;

OUTPUT<=X;

END PROCESS;

END BEHAVE;

NEXT舉例

LOOP1:FOR I IN 7 DOWNTO 0 LOOP

A(I)<='0';

NEXT WHEN(A=B);

A(I)<='1';

END LOOP1;

---成立則跳過此次循環(huán)剩下的語句,進(jìn)行下次循環(huán)

4元素位矢量比較(EXIT)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DEMO1 IS

PORT(

INPUT1: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

INPUT2: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

OUTPUT: OUT STD_LOGIC --0相等,1不相等

);

ARCHITECTURE BEHAVE OF DEMO1 IS

VARIABLE Y:STD_LOGIC;

BEGIN

PROCESS(INPUT1,INPUT2)

Y:='0';

BEGIN

FOR I IN 3 DOWNTO 0 LOOP

Y:='1';--假設(shè)不相等

EXIT WHEN(INPUT1(I)/=INPUT2(I));

Y:='0';--沒有跳出,說明目前還是相等的

END LOOP;

OUTPUT<=Y;

END PROCESS;

END BEHAVE;

半加器造全加器

library ieee;

use ieee.std_logic_1164.all;

entity demo10 is

port (

A, B, Cin : in std_logic;

Sum, Cout : out std_logic

);

end entity demo10;

architecture Behavioral of demo10 is

component Half_Adder

port (

X, Y : in std_logic;

S, C : out std_logic

);

end component;

signal S1, S2, C1, C2 : std_logic;

begin

-- First Half Adder

Half1: Half_Adder port map(A, B, S1, C1);

-- Second Half Adder with Carry In from the first Half Adder

Half2: Half_Adder port map(S1, Cin, Sum, C2);

-- OR gate for Cout

Cout <= C1 or C2;

end architecture Behavioral;

-- Half Adder

library ieee;

use ieee.std_logic_1164.all;

entity Half_Adder is

port (

X, Y : in std_logic;

S, C : out std_logic

);

end entity Half_Adder;

architecture Behavioral of Half_Adder is

begin

S <= X xor Y; -- Sum

C <= X and Y; -- Carry

end architecture Behavioral;

--下面自己寫的

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY BAN IS

PORT(

A,B:IN STD_LOGIC;

S,Y:OUT STD_LOGIC

);

END BAN;

ARCHITECTURE BEHAVE1 OF BAN IS

BEGIN

S<=A OR B;

Y<=A AND B;

END BEHAVE1;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY demo12 IS

PORT(

A,B,C:IN STD_LOGIC;

S,Y:OUT STD_LOGIC

);

END demo12;

ARCHITECTURE BEHAVE OF demo12 IS

COMPONENT BAN IS

PORT(

A,B:IN STD_LOGIC;

S,Y:OUT STD_LOGIC

);

END COMPONENT;

SIGNAL T1,T2,T3:STD_LOGIC;

BEGIN

U1:BAN PORT MAP(A,B,T1,T2);

U2:BAN PORT MAP(T1,C,S,T3);

Y<=T2 OR T3;

END BEHAVE;

四位二進(jìn)制加法計(jì)數(shù)器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNTER IS

PORT(CLK, EN, RST : IN STD_LOGIC;

Q : OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END; --設(shè)置輸入時(shí)鐘信號、時(shí)鐘使能信號和異步清零信號,以及 7 段 LED 數(shù)

碼管輸出使能信號

ARCHITECTURE ONE OF COUNTER IS

SIGNAL R : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(CLK, EN)

BEGIN

IF RST = '1' THEN R <= (OTHERS => '0');

--異步清零功能,位于時(shí)鐘信號判斷之前實(shí)現(xiàn)異步

ELSIF CLK'EVENT AND CLK = '1' THEN

--判斷時(shí)鐘信號此時(shí)是否是上升沿

IF EN = '1' THEN

--判斷是否允許計(jì)數(shù)

R <= R + 1;

END IF;

END IF;

CASE R IS

WHEN "0000" => Q <= "0111111";

WHEN "0001" => Q <= "0000110";

WHEN "0010" => Q <= "1011011";

WHEN "0011" => Q <= "1001111";

WHEN "0100" => Q <= "1100110";

WHEN "0101" => Q <= "1101101";

WHEN "0110" => Q <= "1111101";

WHEN "0111" => Q <= "0000111";

WHEN "1000" => Q <= "1111111";

WHEN "1001" => Q <= "1101111";

WHEN "1010" => Q <= "1110111";

WHEN "1011" => Q <= "1111100";

WHEN "1100" => Q <= "0111001";

WHEN "1101" => Q <= "1011110";

WHEN "1110" => Q <= "1111001";

WHEN "1111" => Q <= "1110001";

WHEN OTHERS => Q <= "0000000";

END CASE;

--通過打表的方式使得對應(yīng)的 4 位二進(jìn)制數(shù)能夠?qū)?yīng)相應(yīng)的 7 段 LED 數(shù)碼管

的使能輸出信號

END PROCESS;

END;

元件例化舉例

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ND2 IS

PORT(

A,B:IN STD_LOGIC;

C:OUT STD_LOGIC

);

END ND2;

ARCHITECTURE BEHAVE1 OF ND2 IS

BEGIN

C<=A NAND B;

END BEHAVE1;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY demo12 IS

PORT(

A,B,C,D:IN STD_LOGIC;

OUTPUT:OUT STD_LOGIC

);

END demo12;

ARCHITECTURE BEHAVE OF demo12 IS

COMPONENT ND2 IS

PORT(

A,B:IN STD_LOGIC;

C:OUT STD_LOGIC

);

END COMPONENT;

SIGNAL OUT1,OUT2:STD_LOGIC;

BEGIN

U1:ND2 PORT MAP(A,B,OUT1);

U2:ND2 PORT MAP(C,D,OUT2);

U3:ND2 PORT MAP(OUT1,OUT2,OUTPUT);

END BEHAVE;

--元件例化語句屬于并行語句,不能放在進(jìn)程里面

浙公網(wǎng)安備 33010602011771號

浙公網(wǎng)安備 33010602011771號