失調電壓(三)運放失調的仿真

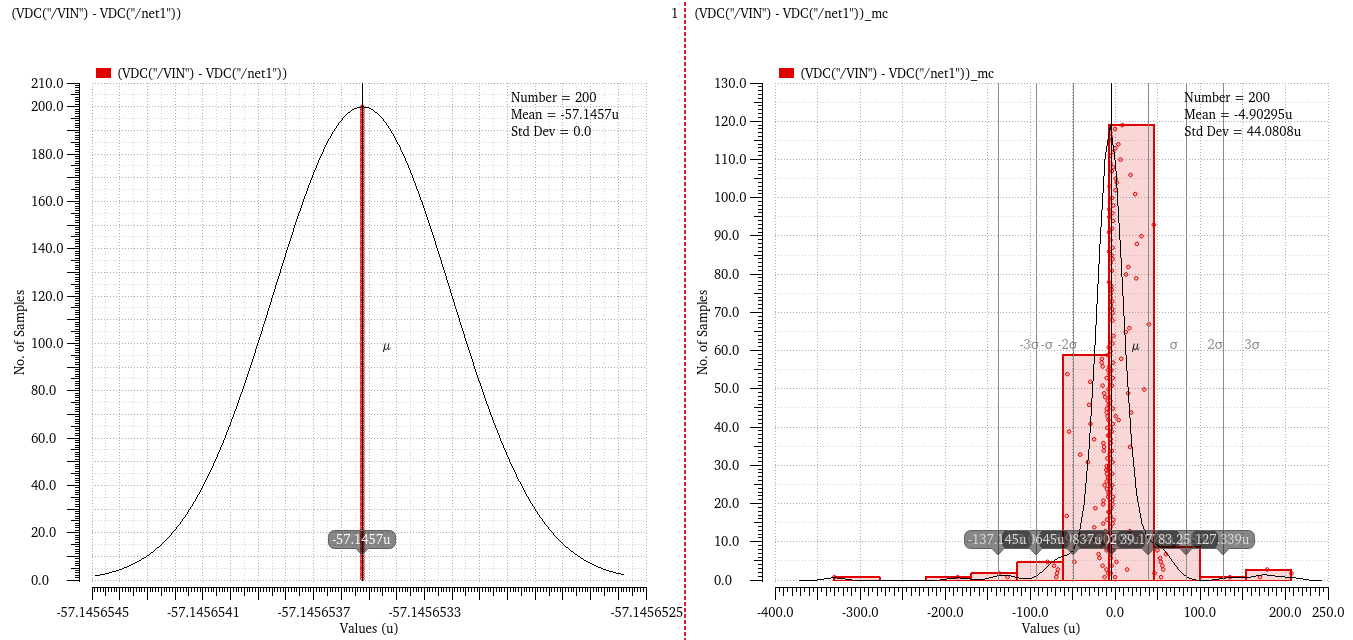

經常在某紅薯/某群看到有同學問為什么他的VOS仿真結果像下面這個樣子,均值uV級,3sigma也是uV級。大家聽后分別表示驚為天人,是不是用了chopper,雖然說我當時用chopper也沒chopper到3sigma50uV的情況。后來發現只是有人沒用帶蒙卡模型的管子去跑了VOS的蒙卡仿真hhhhh。

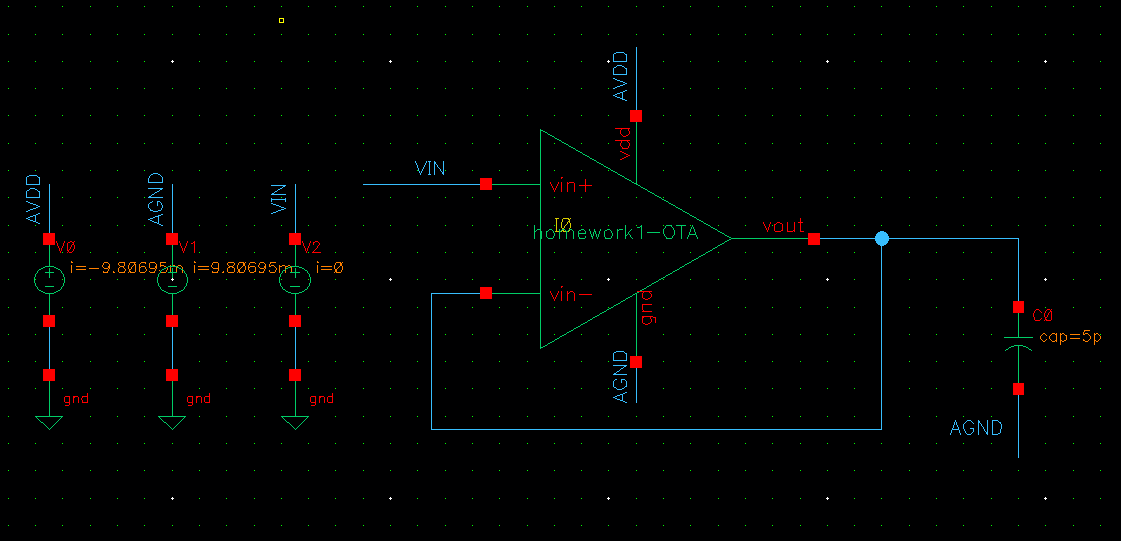

運放失調電壓的仿真我目前用的是Allen書里寫的這種方式,一個最簡單的tb可以搭成這樣(確實是啥都不考慮最簡單的):

由前面(一)(二)的討論可以知道,運放的失調電壓=器件失調=失配+版圖不匹配+電路不匹配。首先,電路不匹配可以體現為不對稱的電路結構、不完全對稱的電流鏡、以及各種buffer由于增益等非理想帶來的系統失調;第二,器件失調引起失調電壓,就像(二)中所說的,一個差動對里面,負載的失配和輸入對管的寬長比失配會被VOD放大到輸出,閾值電壓失配直接折合到輸出,這種道理;另外,版圖畫得匹配性差在此也能引起失調電壓。

因此,要關注失調問題,首先電路本來的系統失調要被關注到,其次要帶上器件的mc模型去跑mc才能仿出失調電壓,最后畫完版圖還要在跑后仿的時候關注到這里的失調電壓是否被一個糟糕的版圖工程師擴大化了。上圖50uV的失調原因現在一目了然,娃沒帶管子的mc模型直接跑的mc,所以其實跑出來的只是個系統失調。

###############################################################################

這里給到一個真實的運放失調仿真結果實例(隨便拿了個很久前的運放,很垃圾但不影響學習):

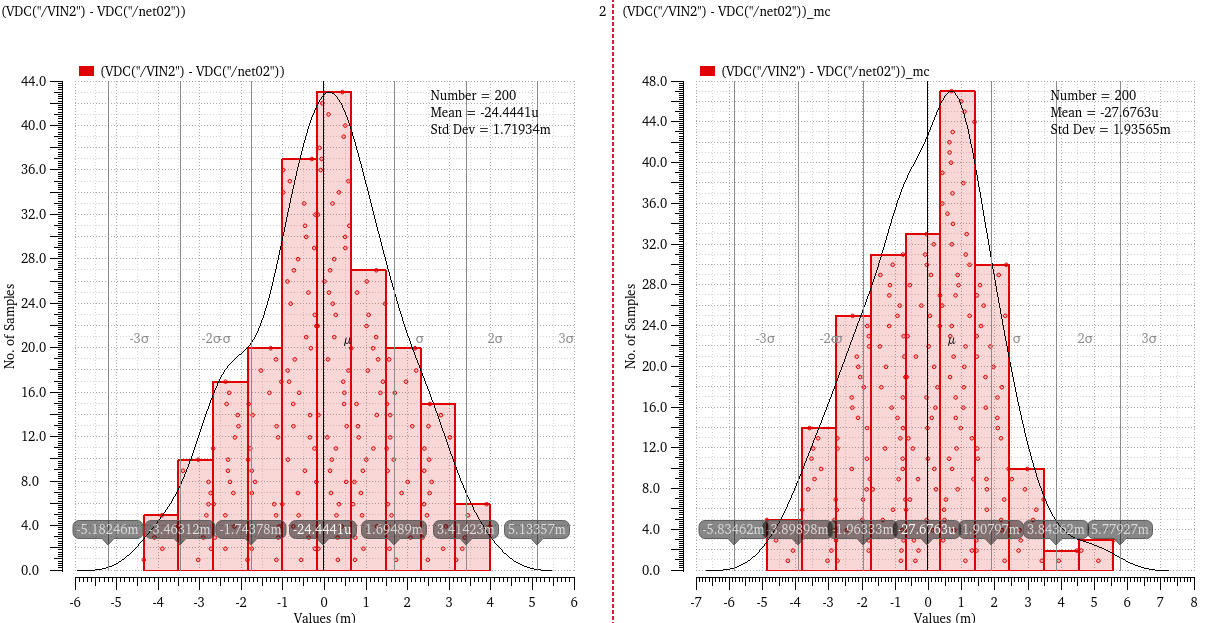

(1)此時,輸入對管的WL=80u2u=160uu,VOD=65mV。仿真到失調電壓的3sigma大約為4.6mV

(2)當我們改輸入對管的WL=160u4u=640uu,VOD=65mV。仿真到失調電壓的3sigma大約為4.4mV。這里為什么增大了輸入對管的面積為4倍,sigma才變化了0.1mV,個人找補原因是,本來就是sqrt的,其次趨勢是對的。

(3)當我們改輸入對管的WL=40u1u=40uu,VOD=65mV。仿真到失調電壓的3sigma大約為5.9mV。這里為減小了輸入對管的面積4倍

(4)當我們改輸入對管的WL=40u2u=80uu,VOD=80mV。仿真到失調電壓的3sigma大約為5.6mV。VOD的影響確實是最明顯的。

就這樣吧,這玩意跟工藝關系太大了,我做過的最好的也只是2mV多,連1mV的邊都碰不到,感覺CMOS工藝要下去到uV內,必須用上clk了,改天再給出chop后的結果。

浙公網安備 33010602011771號

浙公網安備 33010602011771號