嵌入式多核系統的在線分析

概述

盡管多核處理器比單核處理器提供更強大的處理能力,當時多核處理器存在難以檢測和并發(fā)相關的錯誤。本文介紹了一種對多核處理器架構上程序時間測量的全新技術,這種技術通過在目標系統上運行,實現覆蓋率的實時測量和復雜錯誤的分析。

現代汽車上的控制單元已經接管了越來越多的計算密集型任務,而且這種趨勢還沒有結束的跡象。隨著復雜性的增加,錯誤發(fā)生的概率增加,而消除誤差的效率越來越低。 不斷增加的計算負載使得多核處理器的使用成為許多應用的必然。但是,從順序處理到并行處理的轉換可能會引入非常難以再現的錯誤,特別是如果代碼從未打算用于并行執(zhí)行。

毫無疑問,汽車電子行業(yè)需要在軟件開發(fā)和測試方面特別努力,然而,只有能觀察到錯誤的根本原因時,測試和調試環(huán)境才是有意義的。因此,可觀察性是關鍵,與傳統的單核系統相比,現代的多核架構給我們帶來了特殊的挑戰(zhàn)。這樣的系統越集成,就越難以理解軟件內部流程。這正是本文介紹的技術重點解決的問題所在。

經過充分驗證的新技術

軟件插裝被廣泛地應用于軟件內部流程的監(jiān)視,例如,為了測量代碼塊的執(zhí)行時間或者測量覆蓋率,一般采用代碼插裝技術自動在源代碼里插入代碼并記錄程序的執(zhí)行過程。然而,插裝需要占用內存空間并影響程序運行的時間特性。幸運的是,有一種替代方案:幾乎所有的現代處理器都有一個內嵌的跟蹤單元(比如英特爾的Processor Trace),這個跟蹤單元通過指定的接口(比如AGBT)或者標準接口(比如USB DCI、PCIe)進行通信。

圖1: CEDARtools

這個跟蹤單元提供了程序運行流程的信息且并不影響程序的運行。根據處理器架構和跟蹤配置,還可以對程序的時序行為和內存訪問進行重新構建,此外,許多跟蹤單元使得輕量級硬件支持的插裝成為可能,因此可以在發(fā)布代碼中應用,(比如 PTWrite,MIPI STP)同樣也可以用在對外設單元的跟蹤 (內存控制器,通信單元)。

目前常用的嵌入式跟蹤解決方案將寬帶跟蹤數據(幾Gbit/s)存儲在臨時緩沖區(qū)內存中。在測試運行結束時,在PC上重新構建程序流程,并計算結構覆蓋率。這個過程的限制是觀察時間受緩沖區(qū)內存大小的限制,以及離線重建程序流所需的額外計算時間。

實時分析是對離線跟蹤數據分析的進一步改進,需要解決兩項技術難點,一是高壓縮的跟蹤數據流必須要經過處理,CPU的控制流必須要重新構造。這個運算能力必須能夠適高速處理器CPUs (>1 GHz)且適合不同的操作系統。另一方面,產生的事件流必須經過處理,例如,通過記錄跳轉信息來計算結構覆蓋率,或者通過使用在高級語言中配置的數據流處理器來動態(tài)監(jiān)控大量的屬性。

應用實例A:代碼覆蓋率

關鍵安全系統的標準(例如ISO26262)定義了測試過程的需求、所應用的測試技術,以及通過測量測試的結構覆蓋率來驗證這些測試的完整性。對于后者,必須要表明,根據應用的關鍵級別,所有的指令(語句覆蓋了)、所有的跳轉(分支覆蓋率)或者所有的分支條件組合(MC/DC)在測試中都已經被調用了,一般來說,標準在很大程度上保持開放,在不同的測試級別(系統測試、集成測試、模塊測試)驗證對應的結構覆蓋率。理想情況下,需求規(guī)格說明包含在測試中,這樣結構覆蓋率也可以對需求的質量做出證明。

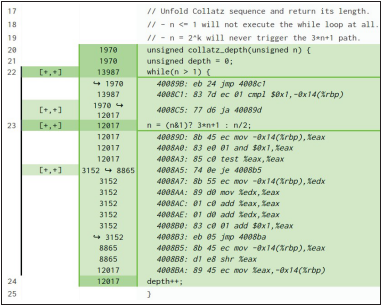

根據CAST-17意見書中所討論的,基于目標碼的結構覆蓋率比基于源代碼的結構覆蓋率提供不同的信息,利用編譯器產生的調試信息,測量出的目標碼覆蓋率可以映射到相應的源代碼覆蓋率,如圖2所示。

圖2:目標碼覆蓋率和源代碼的映射

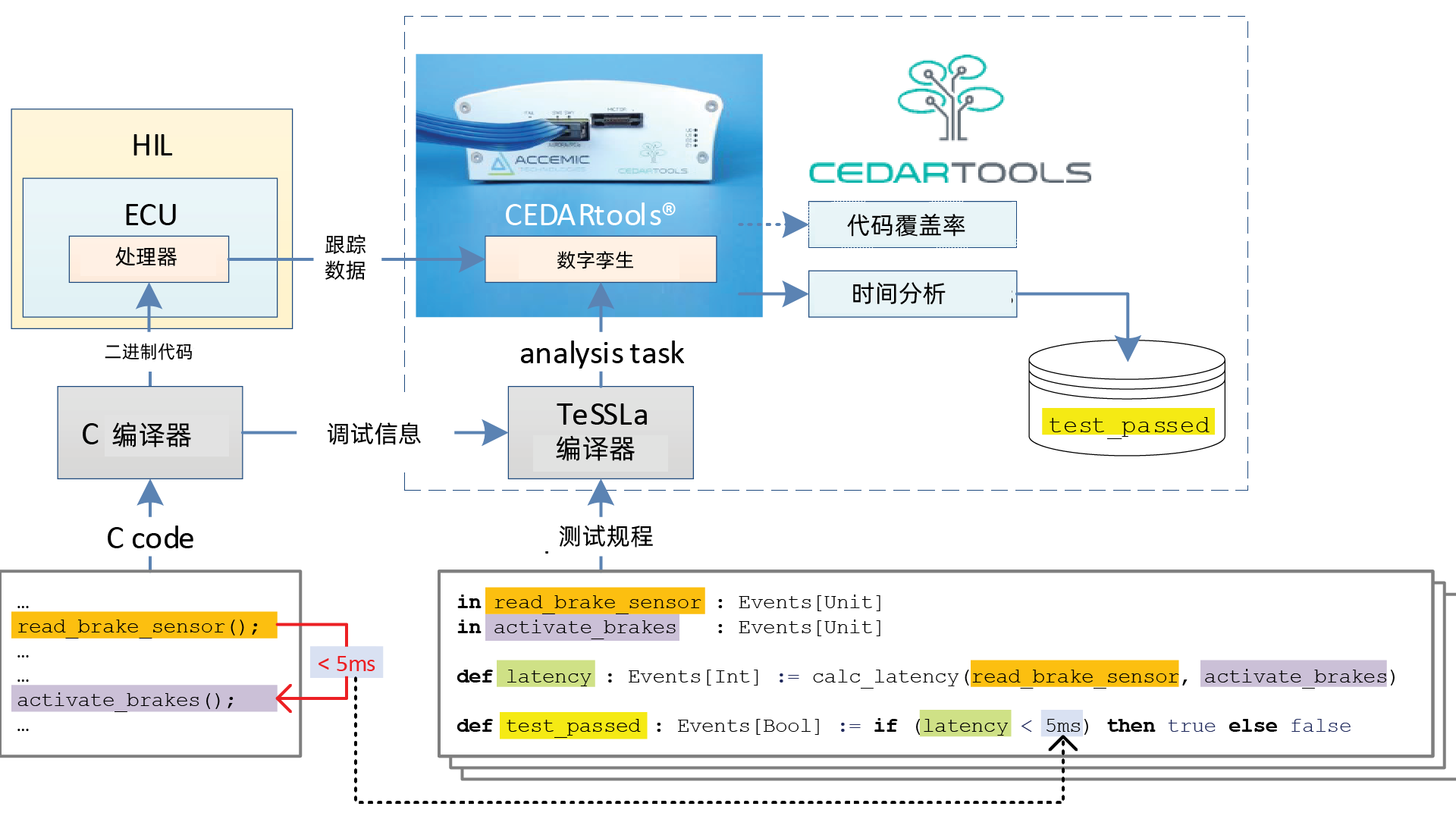

調試信息的分析可以在線實時進行,而不需要任何插裝(因此不會影響目標系統的功能和性能),目標系統的測試覆蓋率可以確定。圖1所示就是這樣的分析系統CEDARtools,利用FPGA進行實時分析。在集成和系統測試期間度量結構化測試覆蓋率能夠識別這些測試中的差距,并替代結構化單元測試。

應用案例B : 動態(tài)分析

靜態(tài)分析是開發(fā)過程中的一個過程或測試方法。嵌入式系統的動態(tài)分析作為靜態(tài)分析的補充顯得越來越重要。而且,這種方法可以通過使用上述硬件實現.

基于這個目的,在持續(xù)重建控制流的過程中對指令地址進行標記,在執(zhí)行這些指令時,特定的事件會自動注入到發(fā)出的事件流中,然后可以在線分析事件流中的特定屬性。所使用的時間處理單元可以利用一種高級語言配置 (www.tessla.io),多種時間屬性(例如,由AUTOSAR TIMEX 或者Amalthea定義) 可以并行監(jiān)視。FPGA只需要參數化事件處理單元,不需要單獨合成邏輯結構,因此,高級語言屬性描述可以在幾秒鐘完成,如圖3所示。

圖3 使用CEDARtools? 進行動態(tài)分析

動態(tài)分析也是調試的強大工具,特別是對于復雜的非確定性錯誤模式。根據發(fā)生的概率和應用領域的不同,尋找這些缺陷可能會需要付出巨大成本和開銷。

設計的考慮

安全規(guī)范中已經規(guī)定了適當的預防措施,在電子控制單元(ECU)的測試期間和發(fā)布后都要具備的全面可觀察性。跟蹤接口應該在測試階段和生產車輛的特定ECU版本中可用。此外,對于生產前和生產后車輛的測試,必須確保從ECU到分析儀(通常位于車內)的跟蹤數據的無干擾傳輸。

結論

隨著嵌入式系統復雜性的提高,產品發(fā)布后缺陷的數量不斷增加,需要應用新的測試方法。這些方法包括結構測試覆蓋率的度量,以及在完全集成的系統中運行時分析的自動執(zhí)行。由于有了這項新技術,現在采用CEDARtools就可以進行這種分析,而且確保不會影響軟件的運行時行為。

此外,即使在發(fā)布系統之后,它也允許有效地分析復雜錯誤的原因。為了能夠使用這種測試分析技術,需要允許對由處理器輸出的跟蹤數據進行寬帶寬訪問。

附加信息1: 動態(tài)軟件架構

汽車軟件的重要性持續(xù)加大,這一趨勢很可能會繼續(xù)下去。特別是在高度自動化的駕駛領域,許多創(chuàng)新都是基于軟件的。與上市時間的壓力相結合,OEM廠商在驗證他們的系統時面臨著各種各樣的挑戰(zhàn)。除了不斷增加的軟件體系結構的復雜性之外,遺留組件的集成以及多核平臺上的聯合調度都是特別棘手的問題。

LET 概念(邏輯執(zhí)行時間)提供了一個框架來應對這些挑戰(zhàn)。但是,它依賴于一個重要的前提條件:必須確保每個任務在指定的時間窗口內安全地處理。靜態(tài)分析目前不能提供足夠的精度。因此,還需要使用測量方法來檢查是否達到了最后期限。不需要軟件插裝的方法在這個環(huán)境中非常有趣,因為這種方法度量了真實的軟件狀態(tài)。

為了簡化設計過程,LET概念通過只查看讀寫訪問的時間,從給定平臺上的物理執(zhí)行時間中抽象出來。只要滿足最后期限,就不考慮實際執(zhí)行時間。

附加信息2:CEDATtools

CEDRAtools是 Accemic Technologies開發(fā)的用以對復雜嵌入式系統分析的工具,它解決了緩沖區(qū)大小受限的問題,目前汽車行業(yè)和航空航天行業(yè)主要的開發(fā)商都在評估和使用這個系統。

這個工具不采用跟蹤數據存儲事后離線分析技術,而是利用先進的硬件實時對上Gbit的數據進行分析,可以實現:

● 對一個或多個CPU的控制流和數據流進行重建,這是一個相當苛刻的任務,因為跟蹤數據是由處理器以高度壓縮的形式輸出。

● 對生成的事件流進行高度可配置的實時分析(例如指令命中、數據訪問、任務更改,最多100個事件/s),同時對多種復雜屬性進行調查(效應鏈的最小和最大運行時間、統計、序列、值范圍的檢查等)。

● 連續(xù)實時測量結構測試覆蓋率,不需要在長時間內收集大量的原始跟蹤數據,以便以后在耗時的過程中進行評估,而是使用預定義的高級語言屬性動態(tài)地分析跟蹤數據。這可以在幾分鐘、幾小時甚至幾天內完成。但是,不需要分發(fā)原始數據:使用復雜觸發(fā)器,可以精確地定義哪些原始數據和事件與分析相關,并存儲在現有的跟蹤緩沖區(qū)(4 GByte)中。

支持的處理器*:

- Arm? Cortex?-A, -R, -M

- Infineon Aurix? TC2xx, TC3xx

- Power Architecture? (including NXP QorIQ? P-/T-Series)

- Intel? Atom? (among others E39x0)

支持的跟蹤接口*:

- 高速串行接口 (Aurora): NEXUS, HSSTP, AGBT

- 標準接口: PCIe, USB

- 并行接口:Mictor, NEXUS

*部分還在開發(fā)中

這項工作是由EU H2020 project 732016 "COEMS" 和BMBF project "ARAMiS 2" (FKZ 01IS16025)基金成立的項目。“CoCoSI”研究項目(BMBF KMU Innovativ, FKZ 01IS19044)與項目合作伙伴Accemic Technologies、Fraunhofer IESE、Heicon和Intel對集成系統中結構測試覆蓋率的測量進行了深入研究。

盡管多核處理器比單核處理器提供更強大的處理能力,當時多核處理器存在難以檢測和并發(fā)相關的錯誤。本文介紹了一種對多核處理器架構上程序時間測量的全新技術,這種技術通過在目標系統上運行,實現覆蓋率的實時測量和復雜錯誤的分析。

盡管多核處理器比單核處理器提供更強大的處理能力,當時多核處理器存在難以檢測和并發(fā)相關的錯誤。本文介紹了一種對多核處理器架構上程序時間測量的全新技術,這種技術通過在目標系統上運行,實現覆蓋率的實時測量和復雜錯誤的分析。

浙公網安備 33010602011771號

浙公網安備 33010602011771號