02.Cortex-M3內核概述--從0學RTOS

Cortex-M3簡介

Cortex-M3是一個32位處理器內核。內部的數據路徑是32位的,寄存器是32位的,存儲器接口也是32位的。CM3采用了哈佛結構,擁有獨立的指令總線和數據總線,可以讓取指與數據訪問并行不悖。這樣一來數據訪問不再占用指令總線,從而提升了性能。為實現這個特性,CM3內部含有好幾條總線接口,每條都為自己的應用場合優化過,并且它們可以并行工作。但是另一方面,指令總線和數據總線共享同一個存儲器空間(一個統一的存儲器系統)。換句話說,不是因為有兩條總線,可尋址空間就變成8GB了。

比較復雜的應用可能需要更多的存儲系統功能,為此CM3提供一個可選的MPU,而且在需要的情況下也可以使用外部的cache。另外在CM3中,Both小端模式和大端模式都是支持的。

CM3內部還附贈了好多調試組件,用于在硬件水平上支持調試操作,如指令斷點,數據觀察點等。另外,為支持更高級的調試,還有其它可選組件,包括指令跟蹤和多種類型的調試接口。

主要特性

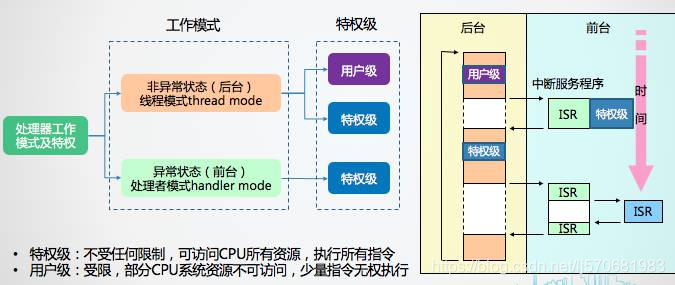

- 工作模式及權限級別

2. 內核寄存器

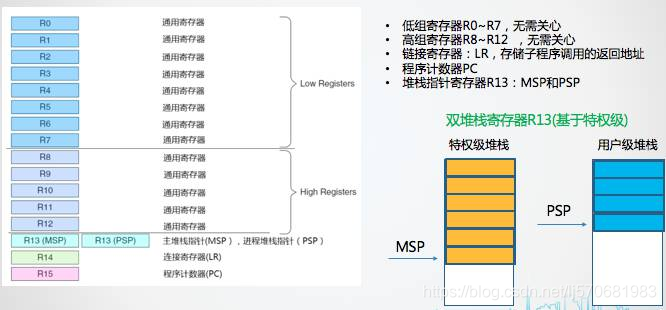

- R14用于存儲子程序調用的返回地址

- R15指明了當前任務執行的指令位置

- R13指明當前任務所用的堆棧位置

- R0~R3主要用于程序調用時,參數的傳遞;執行程序時局部變量的存儲

程序狀態寄存器

3. 存儲器映射

4. 堆棧

M3使用的是 向下生長的滿棧 模型,采用雙堆棧機制。

5. 異常和中斷處理

M3支持的中斷向量表

PendSVC異常

在執行具體的任務切換時,我們在設計中是通過向PendSVC異常發起請求,然后在PendSVC異常處理程序中具體執行任務切換的操作。

異常處理流程比較復雜,我們只需要記往以下幾點:

進入異常

剛進入異常時,硬件自動會將以下寄存器壓入當前堆棧(我們當前用的是PSP)。壓入哪些內容以及他們的次序非常重要!

之后硬件自動跳轉到PendSVC異常處理程序中運行。

退出異常

退出異常時,硬件會自動出棧,這個次序與進入異常時壓棧的順序剛好相反。可以理解為進入異常時保存了部分寄存器狀態,退出時正好恢復。

此外,在退出異常時,我們還會用到EXC_RETURN,其中只用到了0xFFFF_FFFD(即返回異常時進入線程模式,使用PSP堆棧)。

注意,進入異常和退出異常時自動的出入棧會在后面的課時中視為任務部分狀態的保存。

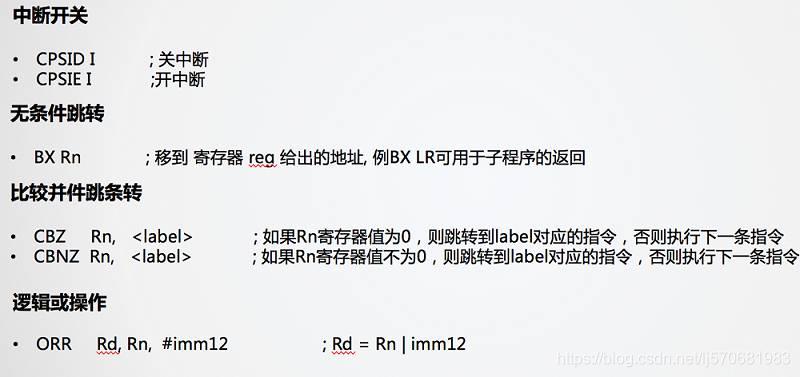

6. 匯編指令

在PendSVC中實現任務切換時,必須要用到一些匯編指令進行狀態保存。課程中只介紹了用到的部分指令。

任務切換的原理

任務的切換主要就是利用系統的PendSV異常。在PendSV中執行RTOS的任務切換。

PendSV異常是作為優先級最低的,即任務切換的優先級低于其他中斷優先級,這樣任務切換要等到其他中斷處理完成后才能處理,并且可以被其他的異常或中斷搶占。

浙公網安備 33010602011771號

浙公網安備 33010602011771號