PCIe掃盲——物理層電氣部分基礎(二)之De-emphasis

這一篇文章中,我們主要來聊一聊PCIe中的信號補償技術(Signal Compensation)——De-emphasis。需要注意的是,Gen1&Gen2與Gen3的De-emphasis實現機制差別較大,而本文只介紹Gen1&Gen2相關內容。如需了解Gen3的相關內容,可自行查閱Gen3的PCIe Spec。

高速信號傳輸中有一個非常棘手的問題,就是當傳輸速率變得越來越高的同時,數據間隔單元(Unit Inerval,UI)也會變得越來越小。這導致前一個bit的數據會對后面bit的數據造成影響,如果不去除這些影響,將會導致誤碼率飆升,甚至通信無法繼續。

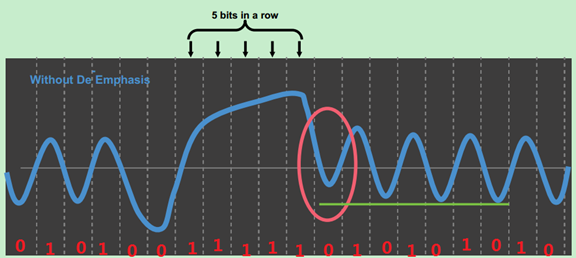

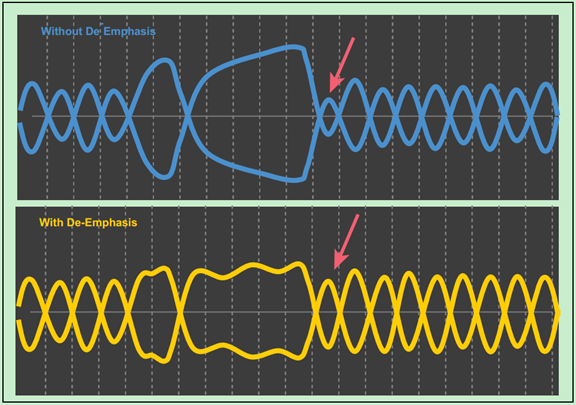

此時,還存在另一個問題,如果系統中出現幾個連續的1(或者0),而接下來的信號為0(或者1)時,信號的電壓可能達不到要求,如下圖所示。這種前面的信號會影響后面的現象,我們稱之為ISI(Inter-Symbol Interference)。產生這種現象的罪魁禍首是傳輸線的介質損耗,具體會在SerDes的專欄文章中詳細介紹。

注:雖然PCIe采用了8b/10b編碼,但是仍然會出現連續的5個0或者5個1(一些控制字符,如COM)。

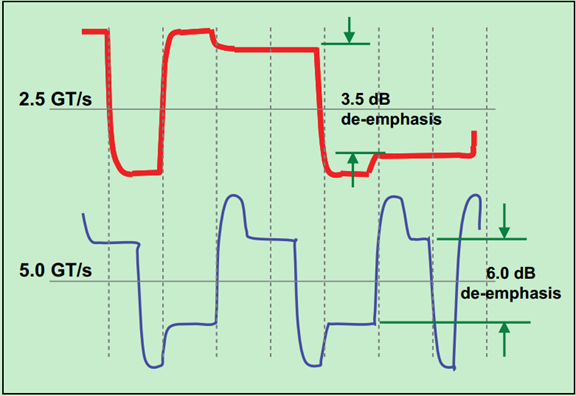

為了解決這個問題,PCIe采用了一種叫做De-emphasis的技術,具體細節如下:

- 當前后電平極性變化時,不使用De-emphasis;

- 連續相同極性電平的第一個bit,不使用De-emphasis;

- 只有連續相同極性電平的第一個bit之后的bit,才使用De-emphasis;

- 對于2.5GT/s,De-emphasis將電壓較少3.5dB。對于5GT/s,則是6dB;

- Beacon信號也需要進行De-emphasis,但是規則稍有差別。

注:Beacon信號在之前關于LTSSM的文章中介紹過。

如下圖所示:

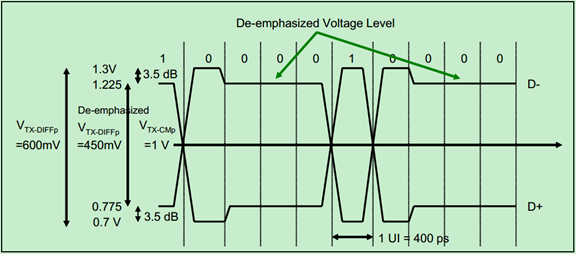

一個De-emphasis的例子如下圖所示:

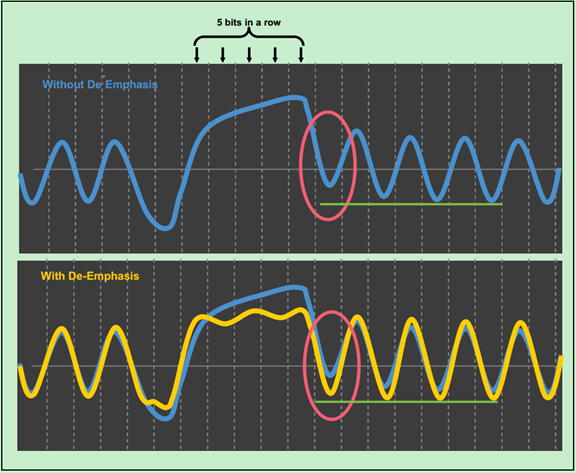

采用De-emphasis之后的PCIe設備接收端信號如下圖所示:

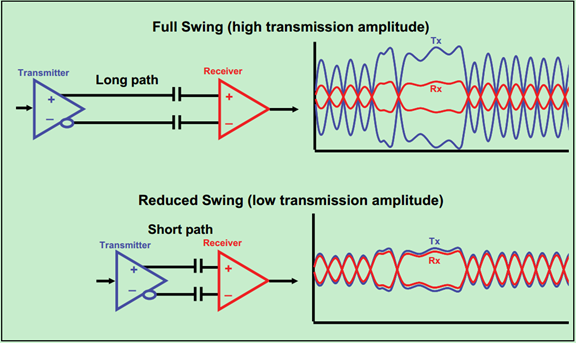

差分的例子:

此外,對于部分使用低擺幅(Reduced Swing)的PCIe設備來說,一般不需要使用De-emphasis。考慮到,這種低擺幅的設備一般傳輸線都比較短(甚至是同一顆芯片/封裝里面),介質損耗相對較小。

浙公網安備 33010602011771號

浙公網安備 33010602011771號