MCU介紹

架構(gòu)

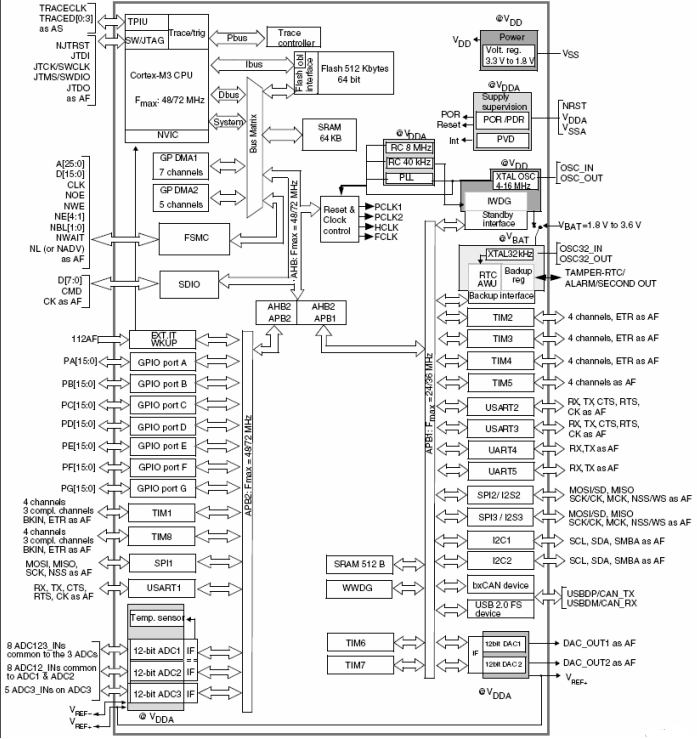

以一個Cortex-M內(nèi)核的STM32 MCU為例,架構(gòu)如圖:

整體可以分成幾個層次:

內(nèi)核

內(nèi)核是MCU的大腦。STM32F1系列MCU使用Cortex‐M3處理器內(nèi)核作為自己的中央處理單元(CPU)。芯片制造商得到CM3處理器內(nèi)核的使用授權(quán)后,就可以把CM3內(nèi)核用在自己的硅片設計中,添加存儲器,外設,I/O以及其它功能塊。ARM提供了現(xiàn)成的、成熟的CPU內(nèi)核架構(gòu)(指令集(Thumb/ARM 指令)、寄存器模型、總線接口、NVIC中斷控制器和調(diào)試協(xié)議(SWD/JTAG)等)。

Cortex‐M3是一個32位處理器內(nèi)核,內(nèi)部的數(shù)據(jù)路徑、寄存器和存儲器接口是32位的。CM3采用了哈佛結(jié)構(gòu),擁有獨立的指令總線和數(shù)據(jù)總線,可以讓取指與數(shù)據(jù)訪問同時進行。擁有R0‐R15的寄存器組,R13是堆棧指針SP,R15是程序計數(shù)寄存器,指向當前的程序地址。簡化視圖如下,包括中斷控制器NVIC,取指單元,解碼單元,算數(shù)運算單元,寄存器組,調(diào)試系統(tǒng),總線接口等。

時鐘與復位系統(tǒng)

時鐘對于嵌入式系統(tǒng)來說等同于人類的心臟。同一個電路,時鐘越快功耗越大,同時抗電磁干擾能力也會越弱,所以復雜的MCU一般都采用多時鐘源,為了保持低功耗工作,主控默認不開啟這些外設功能。用戶可以根據(jù)自己的需要決定芯片要使用的功能,這個功能開關就在各個外設的時鐘。

時鐘源從哪來?以STM32F1為例,包括:

(1)2個外部時鐘源:高速外部振蕩器 HSE (High Speed External Clock signal)外接石英/陶瓷諧振器,頻率為4MHz~16MHz。低速外部振蕩器LSE(Low Speed External Clock signal)外接32.768kHz石英晶體,主要作用于RTC的時鐘源。

(2)2個內(nèi)部時鐘源:高速內(nèi)部振蕩器HSI(High Speed Internal Clock signal)由內(nèi)部RC振蕩器產(chǎn)生,頻率為 8MHz。低速內(nèi)部振蕩器LSI(Low Speed Internal Clock signal)由內(nèi)部RC振蕩器產(chǎn)生,頻率為40kHz,可作為獨立看門狗的時鐘源。

芯片上電時默認由內(nèi)部的HSI時鐘啟動,=可根據(jù)用戶配置切換到對應的外部時鐘源。

鎖相環(huán)是自動控制系統(tǒng)中常用的一個反饋電路,在STM32主控中,鎖相環(huán)的作用主要包括輸入時鐘凈化和倍頻。前者是利用鎖相環(huán)電路的反饋機制實現(xiàn),后者用于使芯片在更高且頻率穩(wěn)定的時鐘下工作。在STM32中,鎖相環(huán)的輸出也可以作為芯片系統(tǒng)的時鐘源。

復位控制器 (Reset Controller):處理上電復位、看門狗復位、軟件復位等。

電源與模擬模塊

電對于嵌入式系統(tǒng)等于血液之于人類。嵌入式常見的低壓電源有3個:

5V

5V通常用作開發(fā)板的主要電源輸入,它是一個通用的電壓標準,適用于大多數(shù)電源適配器和USB電源。可以通過降壓轉(zhuǎn)換器生成其他所需的電壓,如 3.3V 和 1.8V。

外部接口:某些外部接口和外設,如 USB、一些傳感器模塊和顯示模塊,可能需要 5V 電源。

3.3V

IO 電壓:大部分FPGA和SoC的GPIO引腳使用3.3V電壓標準。3.3V是一個常見的電平,可以與很多外部設備和外圍器件兼容,如SPI、I2C和UART接口。

外設供電:許多外設如閃存、SRAM、一些傳感器和通信模塊,也使用 3.3V 電源。

1.8V

內(nèi)核電壓:MCU和SoC的內(nèi)核邏輯通常使用更低的電壓,以減少功耗和發(fā)熱。Xilinx Zynq設備的內(nèi)核邏輯電壓通常為1.8V或更低。

高速接口:某些高速接口,如DDR內(nèi)存和高速串行通信,可能需要1.8V電源。

STM32的工作電壓(VDD)為2.0~3.6V。通過內(nèi)置的電壓調(diào)節(jié)器提供所需的1.8V電源。

安全與控制模塊

看門狗:包括獨立看門狗和窗口看門狗,用于在系統(tǒng)卡住時復位。

錯誤校驗模塊 (ECC, Parity, CRC):保證數(shù)據(jù)傳輸和存儲可靠。循環(huán)冗余校驗(CRC)計算單元是根據(jù)固定的生成多項式得到任一32位全字的CRC計算結(jié)果。

調(diào)試接口

調(diào)試接口 (SWD, JTAG)

總線

總線是嵌入式系統(tǒng)的神經(jīng)網(wǎng)絡,各部件靠它通信。常見的總線有AHB,APB,AXI。AHB/APB橋在AHB和APB總線間提供同步連接。APB操作速度一般最高36MHz,APB2速度一般最高72MHz。在每一次復位以后,所有除SRAM和FLITF以外的外設都被關閉,在使用一個外設之前,必須設置寄存器來打開該外設的時鐘。

Cortex-M內(nèi)核掛在AHB(Advanced High-performance Bus)上。大部分低速外設(GPIO、USART、I2C、SPI、定時器等)掛在APB(Advanced Peripheral Bus)上,通過總線與Cortex內(nèi)核通信。一些高速外設(DMA、以太網(wǎng)、USB、FMC等)掛在AHB或AXI總線上,直接和內(nèi)核或DMA高效交互。AHB和APB通過橋接器連接,形成分層總線結(jié)構(gòu)。

在程序里訪問外設寄存器,Cortex-M內(nèi)核發(fā)出一個AHB總線訪問請求,AHB總線解碼器識別目標地址屬于APB外設區(qū)。請求通過AHB-APB橋轉(zhuǎn)換成APB協(xié)議,最終到達外設寄存器。外設控制器根據(jù)寫入的值驅(qū)動I/O引腳變化。

外設

UART、SPI、I2C、GPIO等。

存儲器映射

STM32F10xxx內(nèi)置64K字節(jié)的靜態(tài)SRAM。它可以以字節(jié)、半字(16位)或全字(32位)訪問。

SRAM的起始地址是0x2000 0000。

512K字節(jié)閃存存儲器(flash)。

程序存儲器、數(shù)據(jù)存儲器、寄存器和輸入輸出端口被組織在同一個4GB的線性地址空間內(nèi)。數(shù)據(jù)字節(jié)以小端格式存放在存儲器中。一個字里的最低地址字節(jié)被認為是該字的最低有效字節(jié),而最高地址字節(jié)是最高有效字節(jié)。

在MCU中,雖然片上實際的Flash、SRAM、外設寄存器都只有幾十KB到幾MB,但ARM內(nèi)核定義了一個統(tǒng)一的32位地址空間(4GB,地址范圍0x0000_0000 ~ 0xFFFF_FFFF),把所有資源都映射進去,形成一個線性地址空間。典型的 Cortex-M 存儲器映射:

地址范圍 | 用途

0x0000_0000 ~ 0x1FFF_FFFF 代碼區(qū)(Code),存放 Flash、ROM

0x2000_0000 ~ 0x3FFF_FFFF SRAM(Data)

0x4000_0000 ~ 0x5FFF_FFFF 外設寄存器(Peripheral,APB/AHB)

0x6000_0000 ~ 0x9FFF_FFFF 外部 RAM/設備(External RAM/Device)

0xA000_0000 ~ 0xDFFF_FFFF 外部設備(External Device)

0xE000_0000 ~ 0xE00F_FFFF 系統(tǒng)控制空間(System Control Space,NVIC,SysTick 等)

0xE010_0000 ~ 0xFFFF_FFFF 保留(Reserved)

這樣設計能夠統(tǒng)一尋址,內(nèi)核用相同的Load/Store指令就能訪問Flash、SRAM、寄存器和I/O端口。也不需要區(qū)分“內(nèi)存訪問”和“I/O 訪問”。外設廠商只要把新的寄存器或存儲器映射到空閑的地址區(qū)間即可。

外設(UART、SPI、I2C、GPIO 等)掛在APB總線上,Cortex內(nèi)核訪問外設時,不是直接跟外設打交道,而是像訪問內(nèi)存一樣,通過總線去讀寫外設的寄存器。

這些外設寄存器被映射(memory-mapped I/O)到MCU的統(tǒng)一地址空間(比如Cortex-M是4GB的地址空間),程序里 (volatile uint32_t)0x40011000 = 0x01; 這種寫操作,就是通過總線把數(shù)據(jù)寫到外設控制器的寄存器,從而控制外設。

其他

DMA控制器,中斷控制器NVIC等。

NVIC(Nested Vectored Interrupt Controller,嵌套向量中斷控制器) 是Cortex-M內(nèi)核里的一個組件,用來管理和響應中斷。NVIC不是一個單獨掛在總線上的外設,它是Cortex-M內(nèi)核里的一部分,和內(nèi)核緊密耦合。外設通過APB總線把中斷信號線拉高/拉低通知NVIC,NVIC根據(jù)配置(優(yōu)先級等)決定是否打斷內(nèi)核當前正在執(zhí)行的代碼,并跳轉(zhuǎn)到向量表里該中斷的 ISR(中斷服務函數(shù))。

作用

中斷響應:當外設(比如 UART、SPI、定時器)產(chǎn)生中斷請求時,NVIC負責接收、判優(yōu)和調(diào)度。

優(yōu)先級管理:支持中斷的優(yōu)先級配置,可以嵌套(高優(yōu)先級中斷打斷低優(yōu)先級中斷)。

中斷屏蔽:可以動態(tài)使能/失能某個中斷。

異常向量表支持:和內(nèi)核一起使用向量表(Vector Table)來找到每個中斷對應的服務函數(shù)入口地址。

如何控制中斷

常見的NVIC寄存器(這些寄存器在 System Control Space (SCS) 里,屬于內(nèi)核區(qū)域,不是普通 APB 外設):

ISER (Interrupt Set-Enable Register):使能某個中斷

ICER (Interrupt Clear-Enable Register):關閉某個中斷

ISPR / ICPR:設置/清除中斷掛起狀態(tài)

IABR:查看中斷是否正在執(zhí)行

IPR (Interrupt Priority Register):設置中斷優(yōu)先級

浙公網(wǎng)安備 33010602011771號

浙公網(wǎng)安備 33010602011771號