GPIO

任何芯片在運行時都要和外部通信,GPIO就是芯片CPU和芯片外部的接口,是由芯片內部寄存器控制的一組可編程的外部引腳接口。

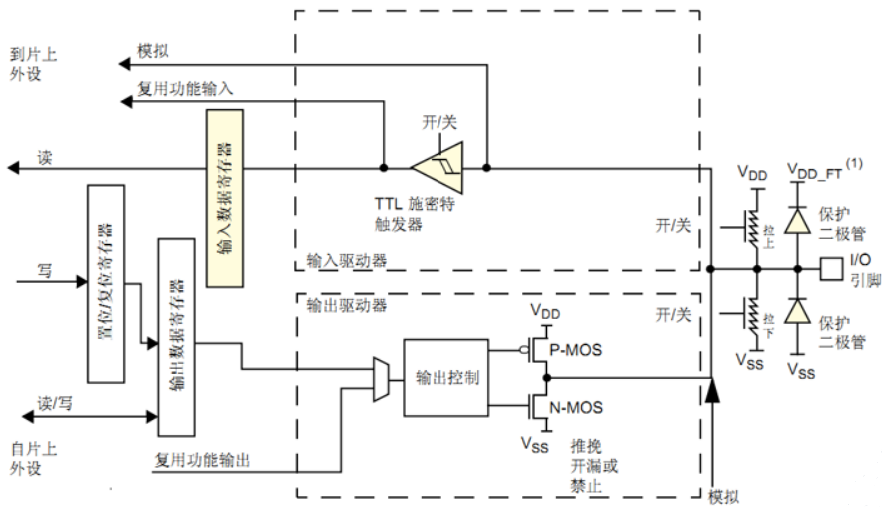

從物理層面來說,GPIO 引腳是芯片封裝上的金屬引腳(或焊盤),直接連接到外部電路。每個引腳內部連著一個可配置的電路單元(輸入緩沖器、輸出驅動器、上拉/下拉電阻等)。這些電路單元的工作模式由 內部寄存器控制。

從寄存器層面來說,芯片內部有一組GPIO控制寄存器,例如:

方向寄存器(DIR/DDR):配置輸入還是輸出

數據輸出寄存器(ODR):輸出高/低電平

數據輸入寄存器(IDR):讀取引腳電平

功能復用寄存器(AFR/MUX):選擇是普通 GPIO 還是外設功能(UART、SPI 等)

上拉/下拉控制寄存器(PUPDR):配置內部上拉/下拉

CPU 修改這些寄存器,就能間接控制引腳的電氣行為。

CPU通過寄存器告訴GPIO電路“這個腳是輸出還是輸入、輸出高還是低”,GPIO電路按指令驅動封裝引腳(或讀取它的狀態)。外部電路通過物理連接與芯片交互。

上圖的I/O引腳就是芯片引腳,其他部分是GPIO的內部結構。

保護二極管

保護二極管用于保護引腳外部過高或過低的電壓輸入。當引腳輸入電壓高于VDD 時,上面的二極管導通,當引腳輸入電壓低于 VSS 時,下面的二極管導通,從而使輸入芯片內部的電壓穩定。這樣的保護很有限,大電壓大電流接入很容易燒壞芯片。在實際的設計中要考慮設計引腳的保護電路。

上拉、下拉電阻

阻值大概在30~50K歐之間,可以通過上、下兩個對應的開關控制。當沒有外部的上、下拉電壓,引腳的電平由引腳內部上、下拉決定。開啟內部上拉電阻工作,引腳電平為高;開啟內部下拉電阻工作,則引腳電平為低。

如果內部上、下拉電阻都不開啟,這種情況就是浮空模式。浮空模式下,引腳的電平是不確定的,引腳的電平可以由外部的上、下拉電平決定。

施密特觸發器(Schmitt Trigger)

把輸入信號“整形”,產生滯回效應,抑制噪聲和毛刺。特別適合處理慢變化或帶抖動的信號(比如機械按鍵、模擬傳感器輸出)。

輸入有兩個閾值:上閾值 Vth+、下閾值 Vth?。當輸入電壓上升到 Vth+ 才切換到高電平;下降到 Vth? 才切換到低電平。中間的小波動不會引起輸出反復跳變。

P-MOS管和N-MOS管

這個結構控制GPIO的開漏輸出和推挽輸出兩種模式。

開漏輸出:輸出端相當于三極管的集電極,要得到高電平狀態需要上拉電阻。

推挽輸出:兩只對稱的MOS管每次只有一只導通,所以導通損耗小、效率高。輸出既可以向負載灌電流,也可以從負載拉電流。推拉式輸出既能提高電路的負載能力,又能提高開關速度。

GPIO 有八種工作模式,四種輸入和四種輸出:

1、輸入浮空

上拉/下拉電阻斷開,施密特觸發器打開,輸出被禁止。IO口的電平完全由外部電路決定。如果IO引腳沒有連接其他的設備,那么檢測其輸入電平是不確定的。該模式可以用于按鍵檢測等情景。

上拉/下拉輸入是給輸入端加一個弱電阻,保證沒有外部信號時,輸入信號不會漂浮。

2、輸入上拉

上拉電阻導通,施密特觸發器打開,輸出被禁止。 當外部沒有信號時,輸入電平被拉到高電平(邏輯 1)。如果外部拉低(比如開關接地),電阻限制電流,輸入變低(邏輯 0)。常用于按鈕、開關輸入。

3、輸入下拉

下拉電阻導通,施密特觸發器打開,輸出被禁止。當外部沒有信號時,輸入端被拉到低電平(邏輯 0)。如果外部拉高(接 VDD),輸入變高(邏輯 1)。常用于需要默認低電平的開關輸入。

4、模擬輸入

上下拉電阻斷開,施密特觸發器關閉,雙MOS管也關閉。其他外設可以通過模擬通道輸入輸出。 該模式下需要用到芯片內部的模擬電路單元單元,用于ADC、DAC、MCO這類操作模擬信號的外設。

5、開漏輸出(Open-Drain)

GPIO內部只保留下拉晶體管(N型MOSFET)。晶體管導通,拉到GND時,輸出低電平;晶體管斷開,輸出懸空,此時外部連接一個上拉電阻到VDD,才能得到高電平。開漏輸出模式下可以讀取IO引腳狀態。適合總線型或多設備共用場景。

常見用途:

I2C 總線,SDA/SCL都是開漏輸出,多個設備可共享一條總線;高電平由上拉電阻生成,低電平由任意設備拉低

中斷/信號線,MCU給外部設備一個信號,但不確定外部電壓,開漏可安全連接不同電壓域

外部驅動器接口,驅動LED、繼電器等外部器件,確保不會短路

6、推挽輸出(Push-Pull Output)

P型和N型晶體管同時驅動,輸出高電平時P型導通,拉到VDD;輸出低電平時N型導通,拉到GND。

常見用途:

普通數字輸出,控制MCU內部或外部邏輯電平,如點亮LED、驅動蜂鳴器等

PWM 輸出,用于電機控制、燈光調光等

高速信號輸出,MCU 內部通信或外設時序信號

直接控制低功耗負載,直接拉高/拉低電壓,無需外部上拉電阻

7、開漏式復用功能、推挽式復用功能

普通GPIO輸出由CPU寫寄存器直接控制引腳高低,復用功能輸出由外設模塊(例如 UART_DR、I2C_DR)控制,CPU 只能間接干預(或者配置外設寄存器)。

每個復用功能可以設置為推挽輸出(Push-Pull)或開漏輸出(Open-Drain)。

浙公網安備 33010602011771號

浙公網安備 33010602011771號