面試必問并發(fā)編程內(nèi)存模型JMM與內(nèi)存屏障剖析 學(xué)習(xí)

總課程:

1、JMM。

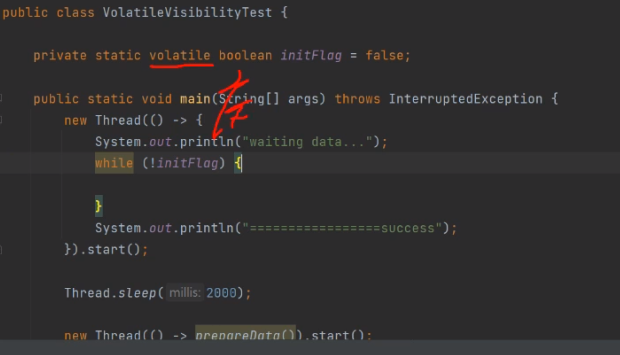

每個(gè)線程會產(chǎn)生一個(gè)變量副本。如下圖所示,第二個(gè)變量修改了變量initFlag,但線程1并不會退出,是因?yàn)槊總€(gè)線程產(chǎn)生了副本。----解決方法:volatile

CPU緩存一致性協(xié)議:MESI機(jī)制,以及內(nèi)存模型底層八大原子操作。

Volatile緩存可見性實(shí)現(xiàn)原理:底層實(shí)現(xiàn)主要通過匯編lock前綴指令,它會鎖定這塊內(nèi)存區(qū)域的緩存(緩存行鎖定),并回寫到主內(nèi)存:

lock指令的解釋:

1、會將當(dāng)前處理器緩存行的數(shù)據(jù)立即寫回到系統(tǒng)主內(nèi)存。

2、通過MESI協(xié)議,這個(gè)寫回內(nèi)存的操作會引起在其他CPU里緩存了該內(nèi)存地址的數(shù)據(jù)無效。

3、提供內(nèi)存屏障功能,使lock前后指令不能重排序。

指令重排序和內(nèi)存屏障。

并發(fā)編程三大特性:可見性、有序性、原子性。

volatile保證可見性與有序性,但是不保證原子性,synchronized可以保證原子性。

指令重排序:在不影響單線程程序執(zhí)行結(jié)果的前提下,計(jì)算機(jī)為了最大限度的發(fā)揮機(jī)器性能, 會對機(jī)器指令重排序優(yōu)化。

重排序遵循的原則:as-if-serial與happens-before原則。

as-if-serial:

不管怎么重排序,單線程程序的執(zhí)行結(jié)果不能被改變。所以編譯器和處理器不會對數(shù)據(jù)依賴關(guān)系的操作做重排序。

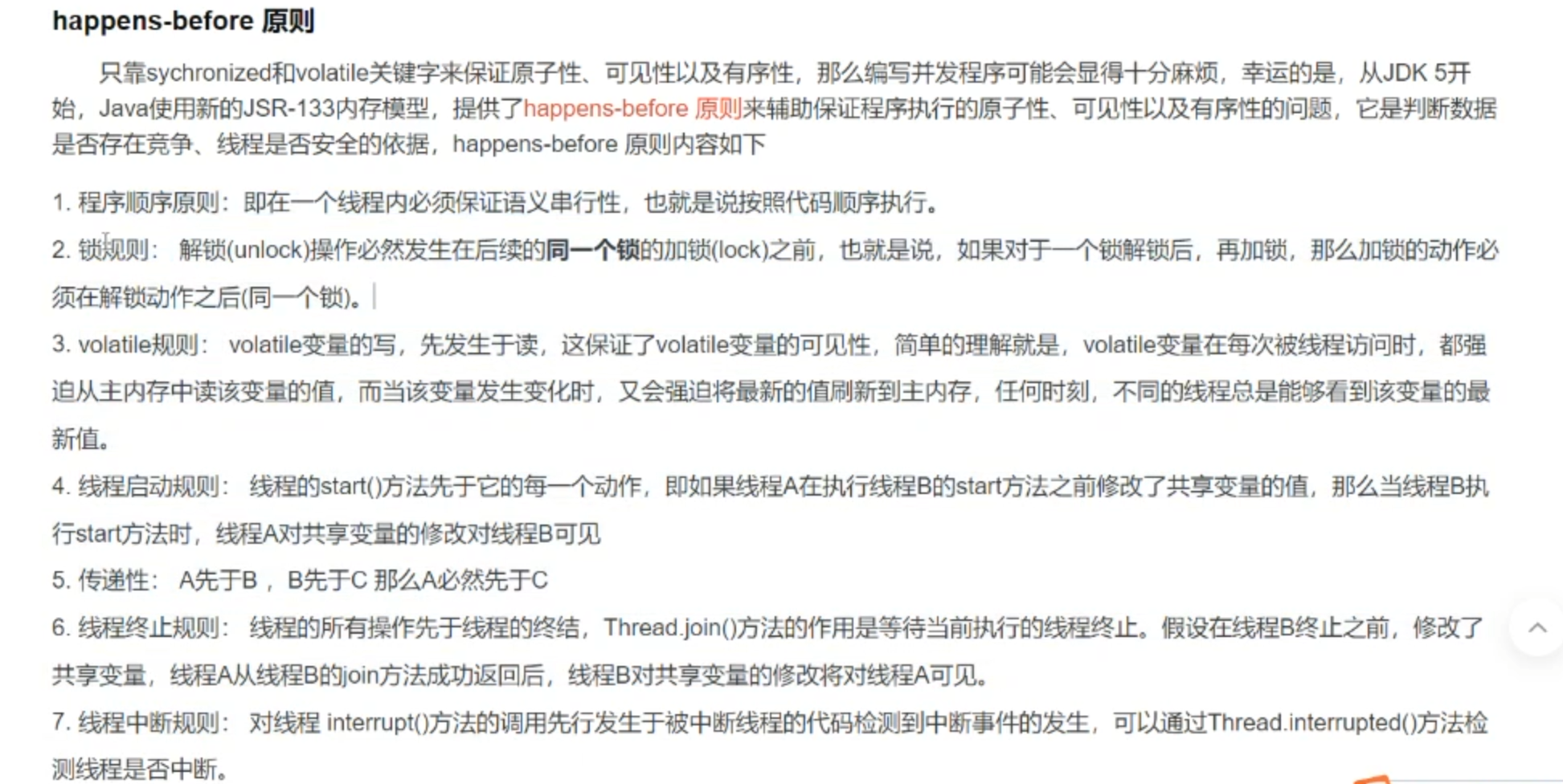

happens-before原則:

浙公網(wǎng)安備 33010602011771號

浙公網(wǎng)安備 33010602011771號