【硬件】一些設計規則

好久不見

距上次更新,以有小半年了,去年九月份至今年三月。幾個月卻勝似滄海桑田,換了人間。原諒我個人的拖延,由于周遭雜事,加上沒有更新的習慣,停更小半年。所幸這小半年也非一無所成,主要的一些成果在硬件體現的較多,當然遺憾也不少,仔細想來,仿佛自己一直被推著走。今年由于考研,估計不會勤更,趁著開學被迫在家線上的空閑,胡亂寫點,想到哪到哪,后面慢慢補充

PCB設計規則

目前而言,我還是很喜歡畫板子的,因為通常情況下,畫出一張好的PCB是經驗積累的成果,受限于層次尚處于入門,只畫些低頻、小功率的板子,自娛自樂,純粹的體力活。當然也積累了一些心得,一點經驗。PCB的繪制規則,個人認為可以從以下三點:信號(SI)、功率(PI)、生產要求,為目的來組成。

信號

一般進行電路分析時,我們慣于采用集總參數模型,即認為導線是純粹理想的、無阻抗的,此時的電路符合基爾霍夫定律;現實中考慮PCB的導線,一般采用分布參數的思路,認為此時的導線符合均勻傳輸線理論。因此對于PCB上的導線,由于其屬于典型的微帶線/帶狀線,符合TEM波傳輸線特征,認為它與外界環境之間電場效應(等效為電容)、磁場效應(等效為電感),相互影響,從而構成了對現實中的PCB導線等效模型,是將分布參數模型轉化為集總參數模型,以方便分析的方法理論。

這也就可以引出主要的幾個設計規則:

1、一般采用135度拐角,而非90度角甚至銳角的走線方式。是為了減少導線中阻抗的突變,導致的反射波,這將極大影響信號質量,因此需要避免阻抗的突變,一般采用135度拐角,高頻下采用圓弧走線,圓弧走線的缺點是不便于密集布局下的布線,不便于后期調整布線。

2、兩層板中,避免頂層和底層的走線平行,甚至重合。類似的,對于敏感的信號線,避免其跨過兩個地層。實際上兩根導線倘若出現重合,二者間實際上形成了一個平板電容器,且由于重合面積較大,擴大電場對信號質量的影響,導致數字信號的電平上升時間變長。一般而言,數字地、模擬地、電源地會選擇進行分割處理,這是由于數字信號一般為方波,存在大量的高頻諧波,容易影響到相對敏感的模擬地,而信號線跨過地層時,實際上兩個地層的電磁環境時不同的,這是信號線的特征阻抗發生突變,違背了原則1。

3、數字地、功率地、模擬地等,一般為了防止相互干擾,會進行分割,二者之間需要一個共同的參考,因此無論如何都需要連在一起,而用什么連,就值得考究了。通常有以下三種器件:0歐姆電阻、磁珠、電感。0歐姆電阻相當于限流通路,寬頻段抑制器,適用于多數情況的地層分割,直流下表現為0歐姆,它對各頻道的突變信號都有抑制作用。磁珠相當于高頻抑制器,直流情況下相當于導線,在特定頻段(一般為高頻)下,有極強的抑制作用,缺點是只對特定頻段有抑制作用,如果對噪聲源的頻段沒有預先了解,磁珠的作用就相當微弱了。電感多用于電源濾波,適用于大功率低頻的場合。磁珠和電感有本質上的區別,電感是儲能元件,而磁珠吸收的能量,會直接以熱量形式散失。

4、給焊盤加淚滴,除了生產要求外,還可以減少阻抗的突變,使得接近焊盤處的阻抗平滑變化,從而提高信號質量。

5、去耦電容應盡可能靠近于元件引腳,以防止過長的導線帶來的過大等效電感。這也是為什么去耦電容一般采用貼片型MLCC,因為其ESL相比引線式要小太多了。

6、差分、蛇形走線是為了阻抗匹配,或者保持電平上升時間的一致性

7、過孔對信號的影響有好有壞,對于信號線而言,應盡可能減少途中過孔數量,由于過孔的導電為內壁導電,其阻抗相對于表面銅線屬于突變,對信號質量有影響。但對于地過孔,可對信號線或晶振進行包地屏蔽處理。

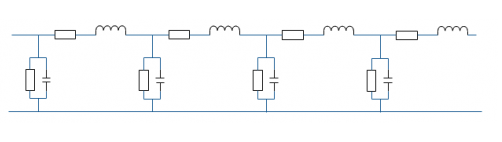

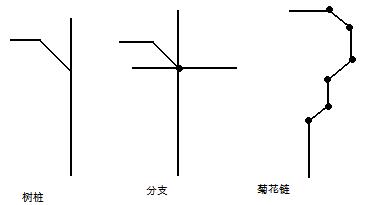

8、對于類似一條線掛接多個設備的情況,一般要避免出現信號線的分叉,而是一條線走完所有點,即菊花鏈

9、

功率

功率規則多數圍繞足夠大的過電流能力展開,

待續

浙公網安備 33010602011771號

浙公網安備 33010602011771號