【Nordic隨筆】nRF54L15的引腳說明

nRF54L15的引腳說明

不同于Nordic的nRF51、nRF52和53系列,nRF54系列,為了功耗做到更加的極致,再nRF54系列上只有一域的概念,通過不同的域管理電源,這樣讓整個CPU處于一個極致高效低能的狀態,達到更低的功耗。

不過這樣子做也帶來了一個小的麻煩,就是不同的域如果跨域使用的話功耗會更高,而且有些引腳是專用引腳,不同于以往的nRF系列IO口自由映射的,所以需要用戶仔細對比芯片規格書的引腳分配章節

所以本篇博客主要是說明nRF54L15&nRF54L10&nRF54L05的引腳分配說明,給大家在前期設計上面避免一些誤區

電源域的劃分

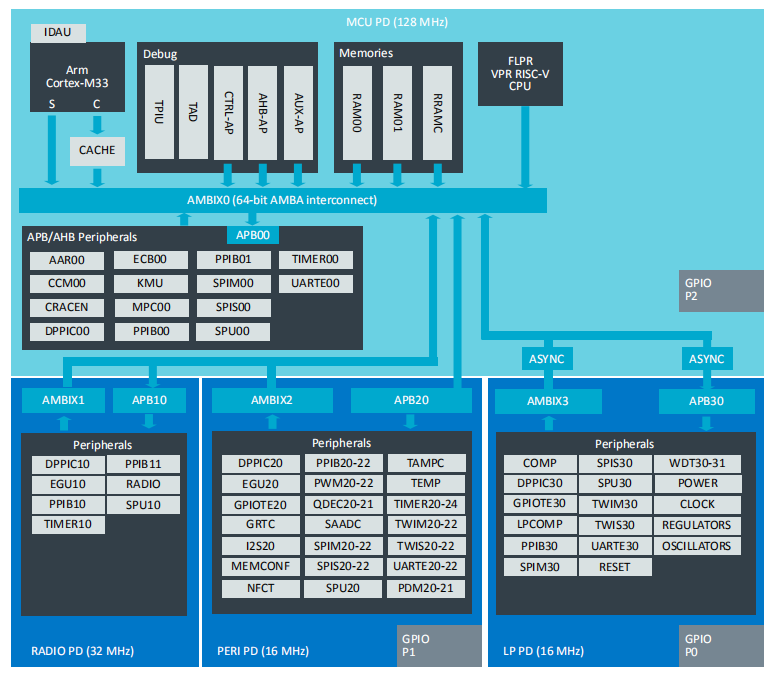

先看一下系統框圖

可以看到整個nRF54L15是劃分了多個區域,接下來講一下各個域的區別

MCU域:這個域主要包含128M 的Arm Cortex-M33和128M的RISC-V的協處理器,以及調試接口,所以他是一個高速域,還包括高速外設(UARTE和HS-SPIM),MCU 域在 128 MHz 時鐘上運行。此域中具有數字 ID 的外圍設備將以數字 0 開頭(例如,UARTE00)。此域有一個專用的 GPIO 端口,即Port2(P2)

LP域:這個是一個低功耗域,他的主頻是16M,主要用作CPU喚醒,這個域可以在MCU睡眠的時候運行,同時這個域只支持數字為30的外設,例如(UART30,SPIS30),注意這個域只用作P0端口

RADIO域:這個域主要是處理Radio的協議棧以及一些其他的短距離協議,例如Thread,2.4G私有協議等。它以32M速率運行,主要是處理RADIO,所以它沒有其他外圍設備處理,也沒有相對應的GPIO端口

PERI域:外設域,這個域主要是處理芯片上面的大部分外設,速率是16MHz,它對應的外設編號是20,例如(UART20,SPI20,TWI20)等,對應的GPIO端口是P1。

上面就是nRF54域的構成和說明,詳細可以看nRF54的規格書

端口功能說明

GPIO port0(P0):

- QFN48有5個IO

- P0的GPIO通信速率最大8M

- 只支持Standard 和 High Drive

- 支持CPU在SYSTEAM_OFF&SYSTEM_ON模式下喚醒

- 支持GPIO喚醒和GPIO口中斷(GPIOTE30)

- 有GRTC的專用引腳,支持PWM_OUT和Colck

GPIO port1(P1):

- QFN48一共有15個引腳:P1.00-P1.14

- 是外設域的專用GPIO口

- 支持8M速率通信

- 只支持Standard 和 High Drive

- 支持CPU在SYSTEAM_OFF&SYSTEM_ON模式下喚醒

- 支持GPIO喚醒和GPIO口中斷(GPIOTE20)

- PWM只能在P1上面使用

- 支持TAMPC(我暫時還不知道是啥)

- 支持模擬輸入引腳 (AIN0-AIN7),由 LP 域中的 ADC (SAADC) 和 COMP/LPCOMP 共享

- 有專用的NFC引腳和RESET引腳,可以設置為通用GPIO(具體怎么設置看我之前的博客)

- 特殊的:如果使用AOA測向和CS信道檢測需要用到搭配RADIO的多天線控制引腳,也是在PI端口上面

-

GPIO port2(P2):

- QFN48一共有11個引腳:P2.00-P0.10

- 此端口上的引腳是芯片上最快的,最大速率支持64M

- 注意用于高速的外設,所以功耗會更高

- 支持standard, high drive, and extra high drive

- P2引腳不能作為喚醒引腳,同時也不能作為GPIO中斷,例如GPIO輸入檢測

- 支持專用外設(UARTE00&SPIM00)

- 有專用的FLPR引腳,可以用來模擬QSPI外設,GPIO口要對應

- P2的部分固定引腳也可以用來做其他外設,但是功耗比較高

下面貼一張圖片總結:

![image]()

引腳分配規則

正常來說,外設編號和CPU域是一一對應的,但是也有例外

1、低功耗(LP)域中的比較器(COMP)/ 低功耗比較器(LPCOMP)必須使用 P1 端口的模擬引腳

2、當外設(PERI)中的通用實時時鐘(GRTC)使用時鐘和 PWM 輸出功能時,需使用 P0 端口的專用引腳

3、P2 端口的部分選定引腳也可被外設(PERI)中的某些串行接口(如 SPIM、SPIS、UARTE)使用,盡管這種配置功耗較高

4、專用時鐘引腳:某些帶有時鐘信號的外設(如 SPI、TWI 和 TRACE)需要使用特定的專用時鐘引腳。這些引腳針對時序進行了優化,并在引腳分配表中用紅色交叉符號標記。所有帶時鐘信號的外設必須使用這些專用引腳,具體看規格書

- 通用 GPIO 用法:所有端口引腳均可作為 GPIO 引腳使用。但 P2 端口的引腳不支持 Sense/DETECT(感知 / 檢測)或 GPIOTE(通用輸入 / 輸出定時器擴展)功能

- 專用引腳分配:

1、FLPR引腳只有P2才有,而且是指定IO口

2、SPIM00(主模式 SPI 接口 00)/UARTE00(增強型 UART 接口 00):必須使用 P2 端口的專用引腳

3、GRTC:若使用時鐘和 PWM 輸出功能,需使用 P0 的專用引腳(P0.03&P0.04);若使用 16MHz 時鐘(CLK16M),則需使用 P1 的專用引腳

4、TAMPC:必須使用 P1 端口的專用引腳

5、NFC:必須使用 P1 端口的專用引腳

6、RADIO:在使用測向(Direction Finding)或信道探測多天線功能時,需使用 P1 端口的專用引腳

7、QSPI引腳:模擬QSPI引腳是固定的不能修改

-固定功能引腳:所有封裝上均有若干固定功能引腳(非 GPIO 引腳)。這些引腳具有不可更改的固定功能,包括:電源和地引腳、晶體振蕩器引腳、去耦和穩壓器引腳、RF 天線引腳(ANT 引腳)、復位引腳和串行線調試引腳

小技巧

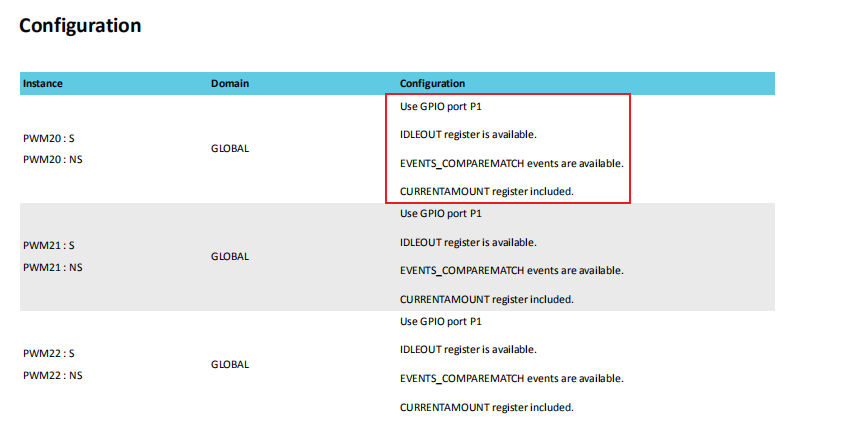

你需要使用什么外設,但是不知道這個域屬于那個部分,或者再代碼使用外設的時候不知道這個外設的編號是什么,可以去對應規格書的外設章節,然后看里面的配置,例如PWM是在P1,而且外設編號分別是PWM20、PWM21、PWM22:

同理SPI也一樣:

資源分享

Nordic的原廠工程師寫了一個網頁nRF54L15引腳分配工具工具"Pin Planner",Pin Planner 工具通過整合數據手冊規則與自動化校驗,將 “避免沖突” 和 “功耗優化” 轉化為可執行的流程。可以結合芯片架構特性(如電源域、專用引腳分配)與工具能力,在前期進行硬件規劃,以規避后期調試中因引腳分配錯誤導致的系統性問題

https://hlord2000.github.io/

總結

nRF54L 的引腳規劃本質是硬件資源與功耗管理的協同設計,在設計之初:優先列出系統所需外設(如 SPI、GRTC),對照數據手冊確認其專用引腳等,注意參考最新版本的數據手冊

芯片規格書鏈接:

https://docs.nordicsemi.com/bundle/ps_nrf54L15/page/keyfeatures_html5.html

如果有項目在做,有需要也可以聯系我將板子的原理圖和PCB Layout 發給我review,或者在論壇提Ticket

浙公網安備 33010602011771號

浙公網安備 33010602011771號