【硬件測試】基于FPGA的8PSK+幀同步系統開發與硬件片內測試,包含高斯信道,誤碼統計,可設置SNR

1.算法硬件測試效果

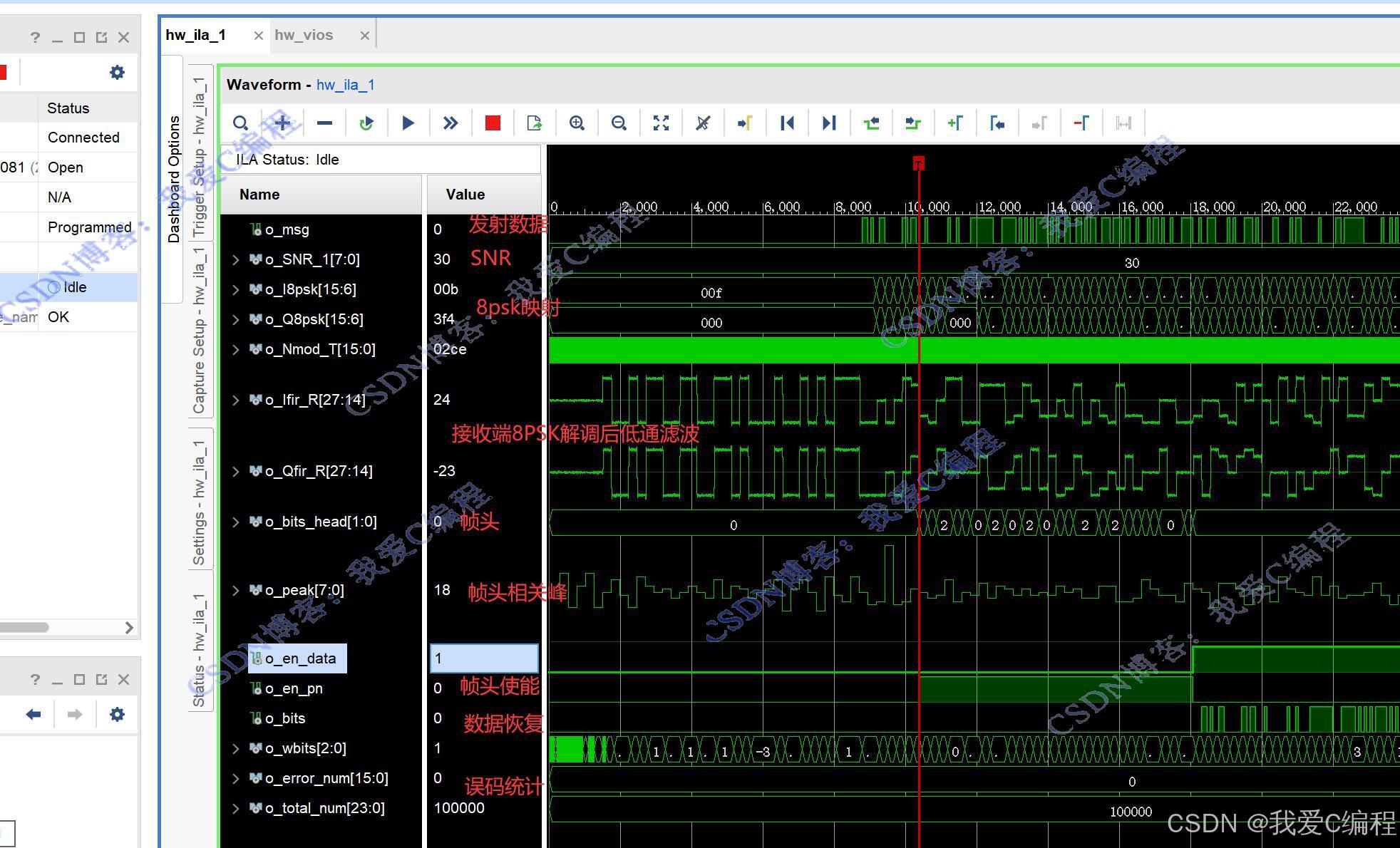

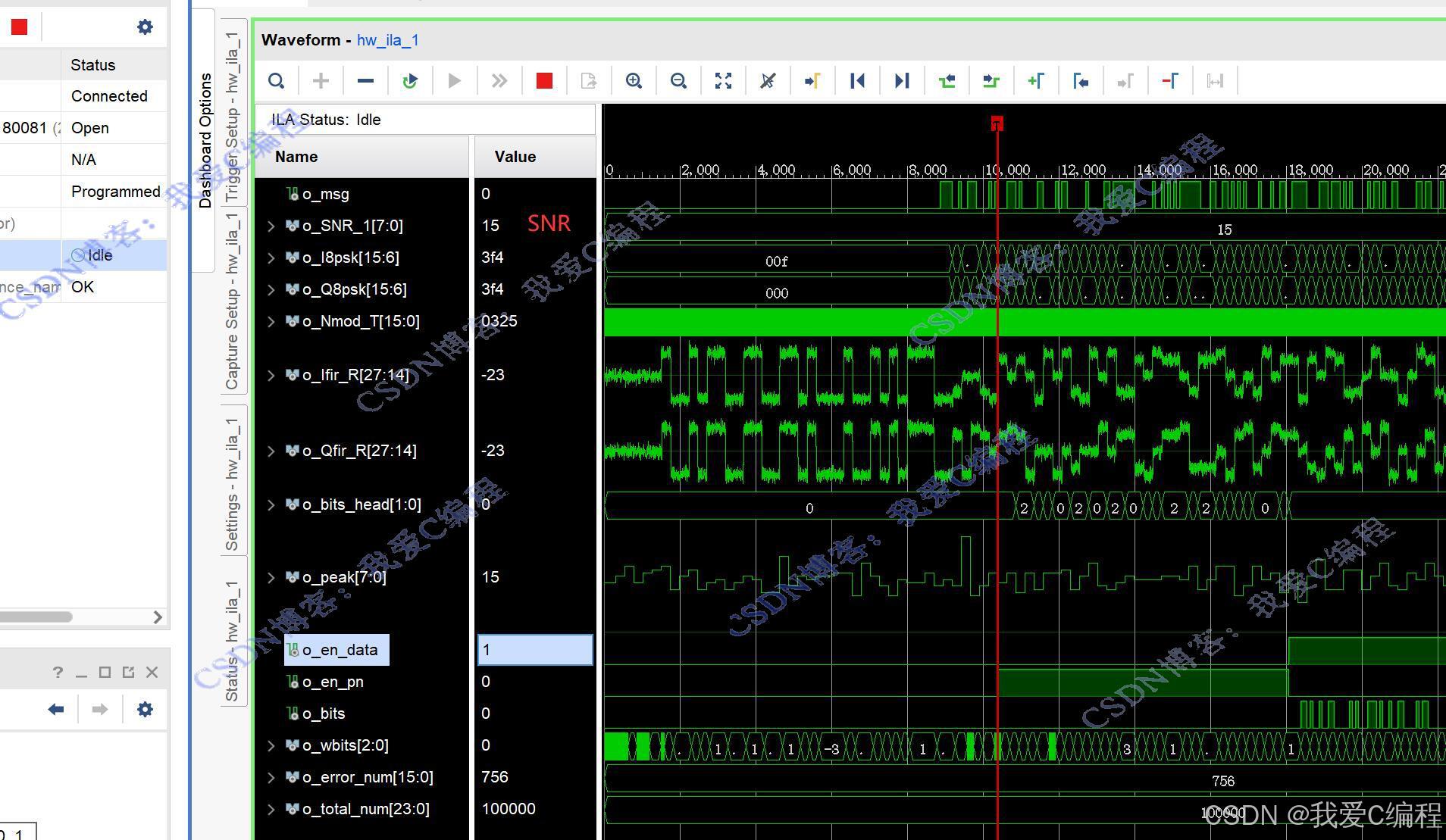

硬件ila測試結果如下:(完整代碼運行后無水印):

vio設置SNR=30db

vio設置SNR=15db

硬件測試操作步驟可參考程序配套的操作視頻。

2.算法涉及理論知識概要

隨著通信技術的不斷發展,相位調制技術因其高頻譜效率和抗干擾能力而廣泛應用于無線通信系統中。其中,8PSK(8相位相移鍵控)作為一種高階調制方式,具有更高的頻譜效率和更強的抗干擾能力,因此備受關注。然而,8PSK調制解調的實現復雜度較高,需要高效的數字信號處理技術。現場可編程門陣列(FPGA)作為一種可編程邏輯器件,具有高度的靈活性和并行處理能力,非常適合實現復雜的數字信號處理算法。

2.1 8PSK調制原理

8PSK調制是一種相位調制方式,其基本原理是通過改變載波的相位來傳遞信息。在8PSK中,一個符號周期內的相位變化有8種可能的狀態,分別對應3個比特的信息。因此,8PSK調制可以看作是一種將3個比特映射到一個符號的映射方式。具體地,假設輸入的比特序列為b2b1b0,則對應的8PSK符號可以表示為:

S(t)=Acos(2πfct+θk) (1)

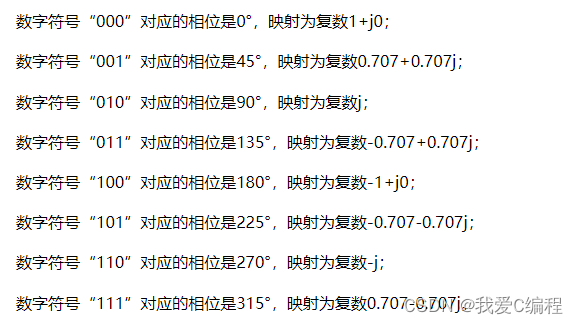

其中,A是載波的振幅,fc是載波的頻率,θk是第k個符號的相位,k=0,1,...,7。θk的取值由輸入的比特序列b2b1b0決定,具體的映射關系如表1所示。

表1:8PSK映射關系

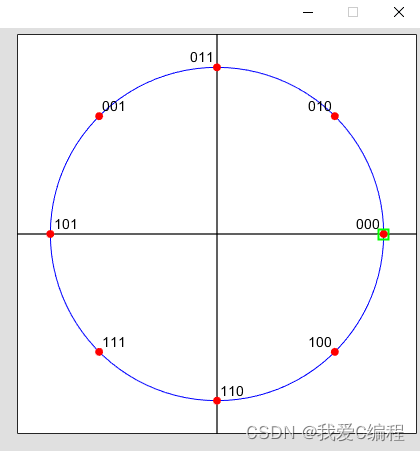

其星座圖如下所示:

2.2 幀同步

在數字通信中,信息通常是以幀為單位進行組織和傳輸的。幀同步的目的是確定每一幀的起始位置,以便接收端能夠正確地解調出每幀中的數據。

設發送的幀結構為:幀同步碼 + 信息碼元序列 。幀同步碼是具有特定規律的碼序列,用于接收端識別幀的起始。

幀同步的過程就是在接收序列中尋找與幀同步碼匹配的位置,一旦找到匹配位置,就確定了幀的起始位置,后續的碼元就可以按照幀結構進行正確的劃分和處理。

3.Verilog核心程序

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2024/11/04 19:54:30

// Design Name:

// Module Name: tops_hdw

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module tops_hdw(

input i_clk,

input i_rst,

output reg [3:0] led

);

//產生模擬測試數據

wire o_msg;

wire[1:0]o_en;

signal signal_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.o_bits(o_msg),

.o_en (o_en)

);

//設置SNR

wire signed[7:0]o_SNR;

vio_0 your_instance_name (

.clk(i_clk), // input wire clk

.probe_out0(o_SNR) // output wire [7 : 0] probe_out0

);

wire[2:0]o_ISET;

wire signed[15:0]o_I8psk;

wire signed[15:0]o_Q8psk;

wire signed[15:0]o_Ifir_T;

wire signed[15:0]o_Qfir_T;

wire signed[31:0]o_mod_T;

wire signed[15:0]o_Nmod_T;

wire signed[31:0]o_modc_R;

wire signed[31:0]o_mods_R;

wire signed[31:0]o_Ifir_R;

wire signed[31:0]o_Qfir_R;

wire [2:0]o_wbits;

wire o_bits;

wire [1:0]o_bits_head;

wire [7:0]o_peak;

wire o_en_data;

wire o_en_pn;

wire o_frame_start;

wire signed[31:0]o_error_num;

wire signed[31:0]o_total_num;

TOPS_8PSK TOPS_8PSK_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.i_SNR (o_SNR),

.i_en (o_en),

.i_dat (o_msg),

.o_ISET (o_ISET),

.o_I8psk(o_I8psk),

.o_Q8psk(o_Q8psk),

.o_Ifir_T (o_Ifir_T),

.o_Qfir_T (o_Qfir_T),

.o_mod_T (o_mod_T),

.o_Nmod_T(o_Nmod_T),

.o_modc_R (o_modc_R),

.o_mods_R (o_mods_R),

.o_Ifir_R (o_Ifir_R),

.o_Qfir_R (o_Qfir_R),

.o_wbits(o_wbits),

.o_bits (o_bits),

.o_bits_head(o_bits_head),

.o_peak(o_peak),

.o_en_data(o_en_data),

.o_en_pn(o_en_pn),

.o_frame_start(o_frame_start),

.o_error_num(o_error_num),

.o_total_num(o_total_num)

);

//ila篇內測試分析模塊140

//ila篇內測試分析模塊140

ila_0 ila_u (

.clk(i_clk), // input wire clk

.probe0({

o_msg,o_SNR,o_I8psk[15:6],o_Q8psk[15:6],//30

o_Nmod_T,o_Ifir_R[27:14],o_Qfir_R[27:14],o_wbits,//48

o_error_num[15:0],o_total_num[23:0],//40

//28

o_en_pn,

o_en_data,

o_peak,

o_bits_head,

o_bits

})

);

endmodule

0sj2_065m

4.開發板使用說明和如何移植不同的開發板

注意:硬件片內測試是指發射接收均在一個板子內完成,因此不需要定時同步模塊。

在本課題中,使用的開發板是:

如果你的開發板和我的不一樣,可以參考代碼包中的程序移植方法進行移植。

5.完整算法代碼文件獲得

V

浙公網安備 33010602011771號

浙公網安備 33010602011771號