【硬件測(cè)試】基于FPGA的4FSK+幀同步系統(tǒng)開發(fā)與硬件片內(nèi)測(cè)試,包含高斯信道,誤碼統(tǒng)計(jì),可設(shè)置SNR

1.算法硬件測(cè)試效果

本文是之前寫的文章

《基于FPGA的4FSK+幀同步系統(tǒng)verilog開發(fā),包含testbench,高斯信道,誤碼統(tǒng)計(jì),可設(shè)置SNR》

的硬件測(cè)試版本。

在系統(tǒng)在仿真版本基礎(chǔ)上增加了ila在線數(shù)據(jù)采集模塊,vio在線SNR設(shè)置模塊,數(shù)據(jù)源模塊。

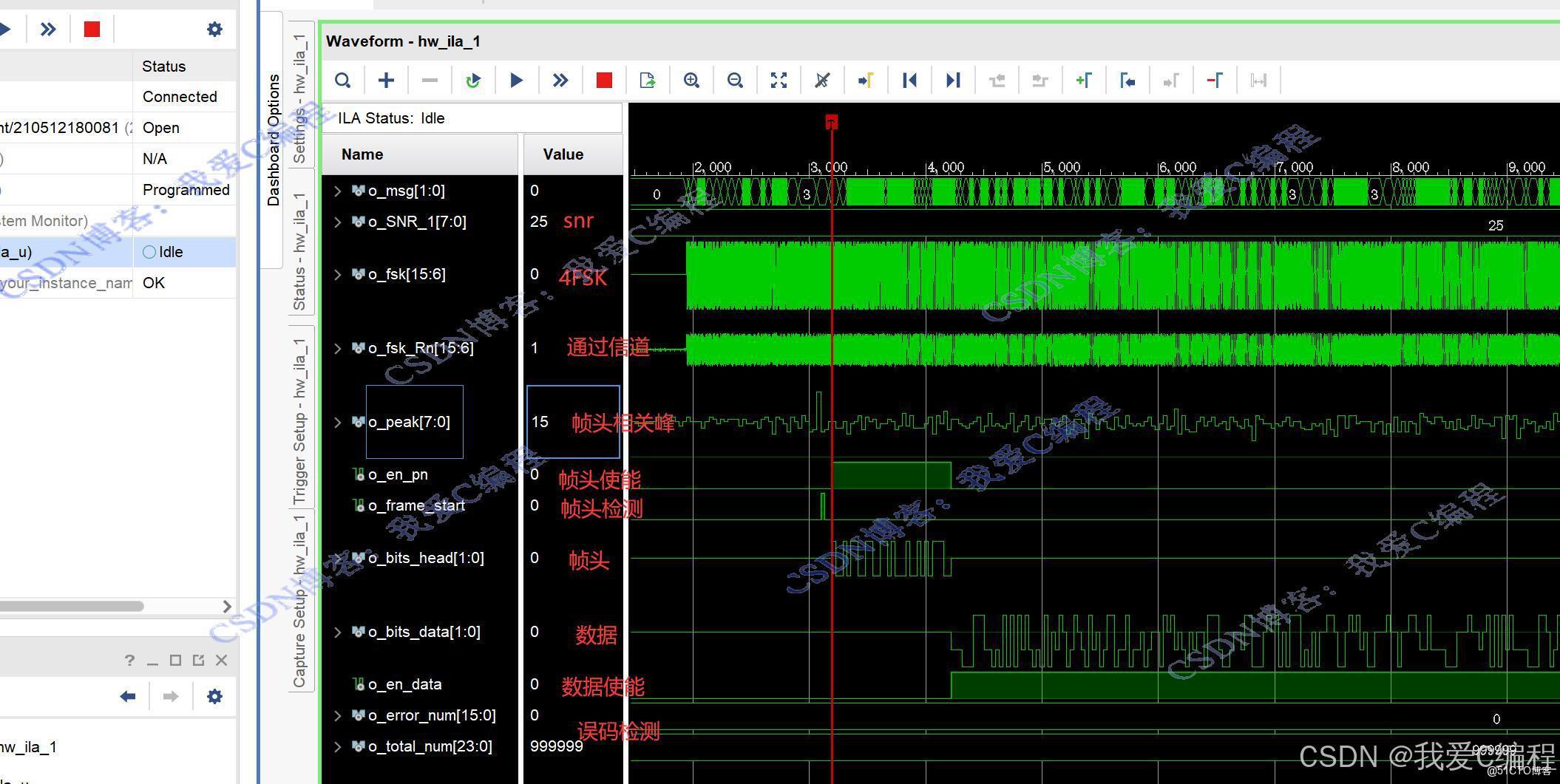

硬件ila測(cè)試結(jié)果如下:(完整代碼運(yùn)行后無水印):

vio設(shè)置SNR=25db

vio設(shè)置SNR=10db

局部放大:

硬件測(cè)試操作步驟可參考程序配套的操作視頻。

2.算法涉及理論知識(shí)概要

四頻移鍵控(4FSK)是一種常用的數(shù)字調(diào)制方法,具有較高的頻帶利用率和抗干擾性能。它利用不同的頻率來傳輸二進(jìn)制數(shù)據(jù),通常應(yīng)用于無線通信和數(shù)據(jù)傳輸?shù)阮I(lǐng)域。

2.1 原理與數(shù)學(xué)公式

4FSK調(diào)制的基本原理是將輸入的二進(jìn)制數(shù)據(jù)轉(zhuǎn)換為不同頻率的信號(hào),以實(shí)現(xiàn)數(shù)據(jù)的傳輸。解調(diào)則是將接收到的不同頻率的信號(hào)還原為原始的二進(jìn)制數(shù)據(jù)。

在4FSK調(diào)制中,輸入的二進(jìn)制數(shù)據(jù)被分為兩組,每組有兩個(gè)比特。根據(jù)這兩個(gè)比特的值,選擇相應(yīng)的頻率輸出。具體來說,有四個(gè)頻率f1、f2、f3、f4與之對(duì)應(yīng),每個(gè)頻率都代表一個(gè)二進(jìn)制組合(00、01、10、11),即十進(jìn)制的0,1,2,3。

頻率選擇:根據(jù)輸入的比特組合選擇相應(yīng)的頻率輸出。例如,當(dāng)輸入為“00”時(shí),選擇頻率f1;當(dāng)輸入為“01”時(shí),選擇頻率f2;當(dāng)輸入為“10”時(shí),選擇頻率f3;當(dāng)輸入為“11”時(shí),選擇頻率f4。

調(diào)制信號(hào):將選擇的頻率進(jìn)行幅度調(diào)制,以便在傳輸過程中具有更好的抗干擾性能。通常采用開關(guān)鍵控(OOK)或脈沖幅度調(diào)制(PAM)等方法進(jìn)行幅度調(diào)制。

解調(diào)信號(hào):在接收端,根據(jù)不同頻率的信號(hào)進(jìn)行解調(diào)。首先通過帶通濾波器將所需的頻率信號(hào)提取出來,然后通過解調(diào)器將其還原為原始的二進(jìn)制數(shù)據(jù)。解調(diào)方法通常采用相干解調(diào)或非相干解調(diào)。

2.2 幀同步

在數(shù)字通信中,信息通常是以幀為單位進(jìn)行組織和傳輸?shù)摹降哪康氖谴_定每一幀的起始位置,以便接收端能夠正確地解調(diào)出每幀中的數(shù)據(jù)。

設(shè)發(fā)送的幀結(jié)構(gòu)為:幀同步碼 + 信息碼元序列 。幀同步碼是具有特定規(guī)律的碼序列,用于接收端識(shí)別幀的起始。

幀同步的過程就是在接收序列中尋找與幀同步碼匹配的位置,一旦找到匹配位置,就確定了幀的起始位置,后續(xù)的碼元就可以按照幀結(jié)構(gòu)進(jìn)行正確的劃分和處理。

3.Verilog核心程序

//產(chǎn)生模擬測(cè)試數(shù)據(jù)

wire signed[1:0]o_msg;

wire o_en;

signal signal_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.o_bits(o_msg),

.o_en (o_en)

);

//設(shè)置SNR

wire signed[7:0]o_SNR;

vio_0 your_instance_name (

.clk(i_clk), // input wire clk

.probe_out0(o_SNR) // output wire [7 : 0] probe_out0

);

reg signed[7:0]i_SNR;

wire signed[15:0]o_carrier1;

wire signed[15:0]o_carrier2;

wire signed[15:0]o_carrier3;

wire signed[15:0]o_carrier4;

wire signed[15:0]o_fsk;

wire signed[15:0]o_fsk_Rn;

wire [1:0]o_bits_data;//數(shù)據(jù)

wire [1:0]o_bits_head;//幀頭

wire [7:0]o_peak;//幀頭檢測(cè)峰值

wire o_en_data;//數(shù)據(jù)使能

wire o_en_pn;//幀頭使能

wire o_frame_start;//幀檢測(cè)標(biāo)記

wire signed[31:0]o_error_num;

wire signed[31:0]o_total_num;

FSK uut(

.i_clk(i_clk),

.i_rst(~i_rst),

.i_en(o_en),

.i_SNR(o_SNR),

.i_bits(o_msg),

.o_carrier1(o_carrier1),

.o_carrier2(o_carrier2),

.o_carrier3(o_carrier3),

.o_carrier4(o_carrier4),

.o_fsk(o_fsk),

.o_fsk_Rn(o_fsk_Rn),

.o_de_fsk1(),

.o_de_fsk2(),

.o_de_fsk3(),

.o_de_fsk4(),

.o_bits(),

.o_bits_data (o_bits_data),

.o_bits_head (o_bits_head),

.o_peak (o_peak),

.o_en_data (o_en_data),

.o_en_pn (o_en_pn),

.o_frame_start (o_frame_start),

.o_error_num (o_error_num),

.o_total_num (o_total_num)

);

//ila篇內(nèi)測(cè)試分析模塊140

ila_0 ila_u (

.clk(i_clk), // input wire clk

.probe0({

o_msg,o_SNR,o_fsk[15:6],o_fsk_Rn[15:6],//30

o_error_num[15:0],o_total_num[23:0],//40

//14

o_en_pn,o_frame_start,

o_en_data,

o_peak,

o_bits_head,

o_bits_data

})

);

endmodule

浙公網(wǎng)安備 33010602011771號(hào)

浙公網(wǎng)安備 33010602011771號(hào)